Advanced-control timer (TIM1) RM0444

592/1390 RM0444 Rev 5

21.4.5 TIM1 status register (TIM1_SR)

Address offset: 0x10

Reset value: 0x0000 0000

Bit 2 CC2IE: Capture/Compare 2 interrupt enable

0: CC2 interrupt disabled

1: CC2 interrupt enabled

Bit 1 CC1IE: Capture/Compare 1 interrupt enable

0: CC1 interrupt disabled

1: CC1 interrupt enabled

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled

1: Update interrupt enabled

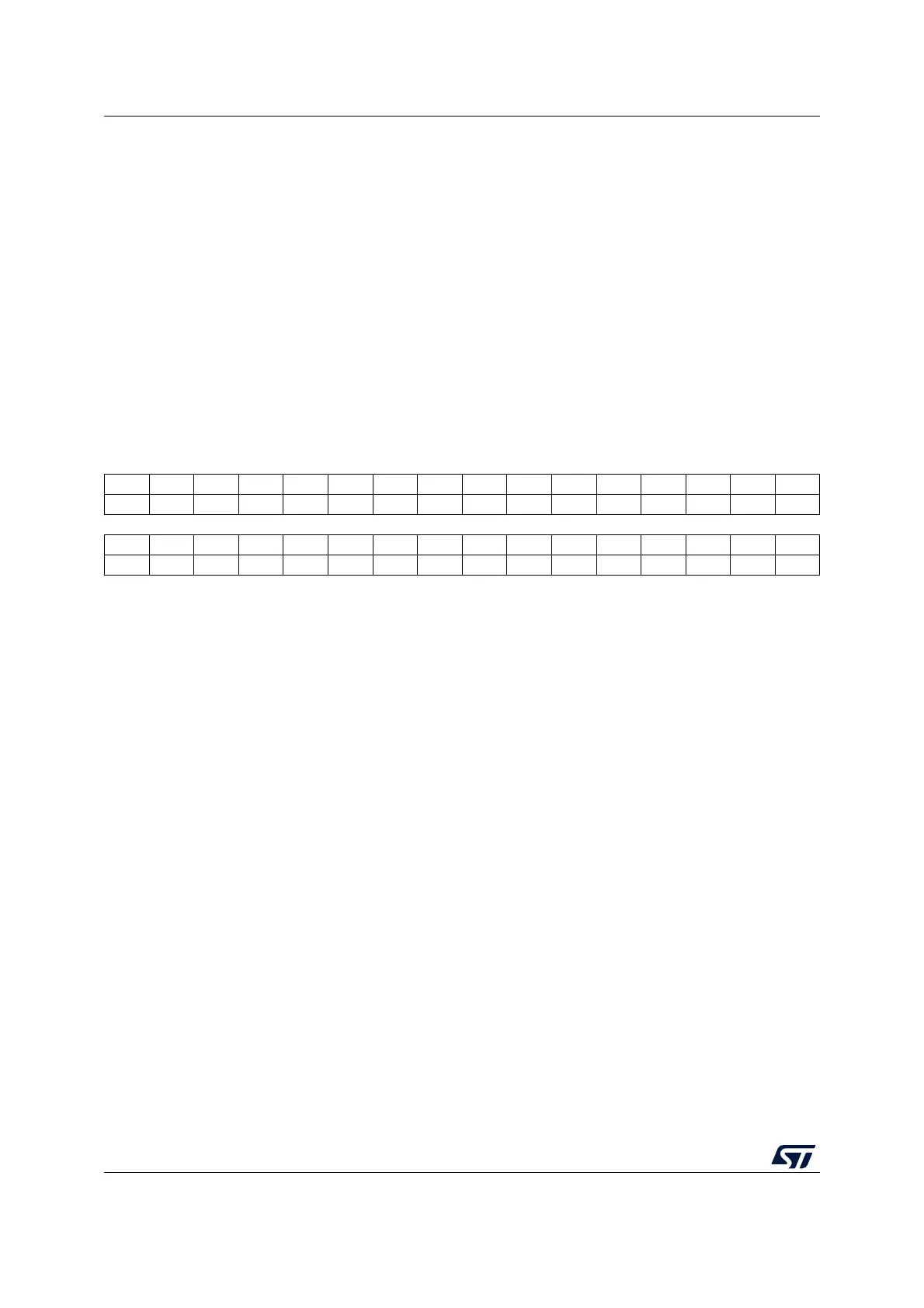

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CC6IF CC5IF

rc_w0 rc_w0

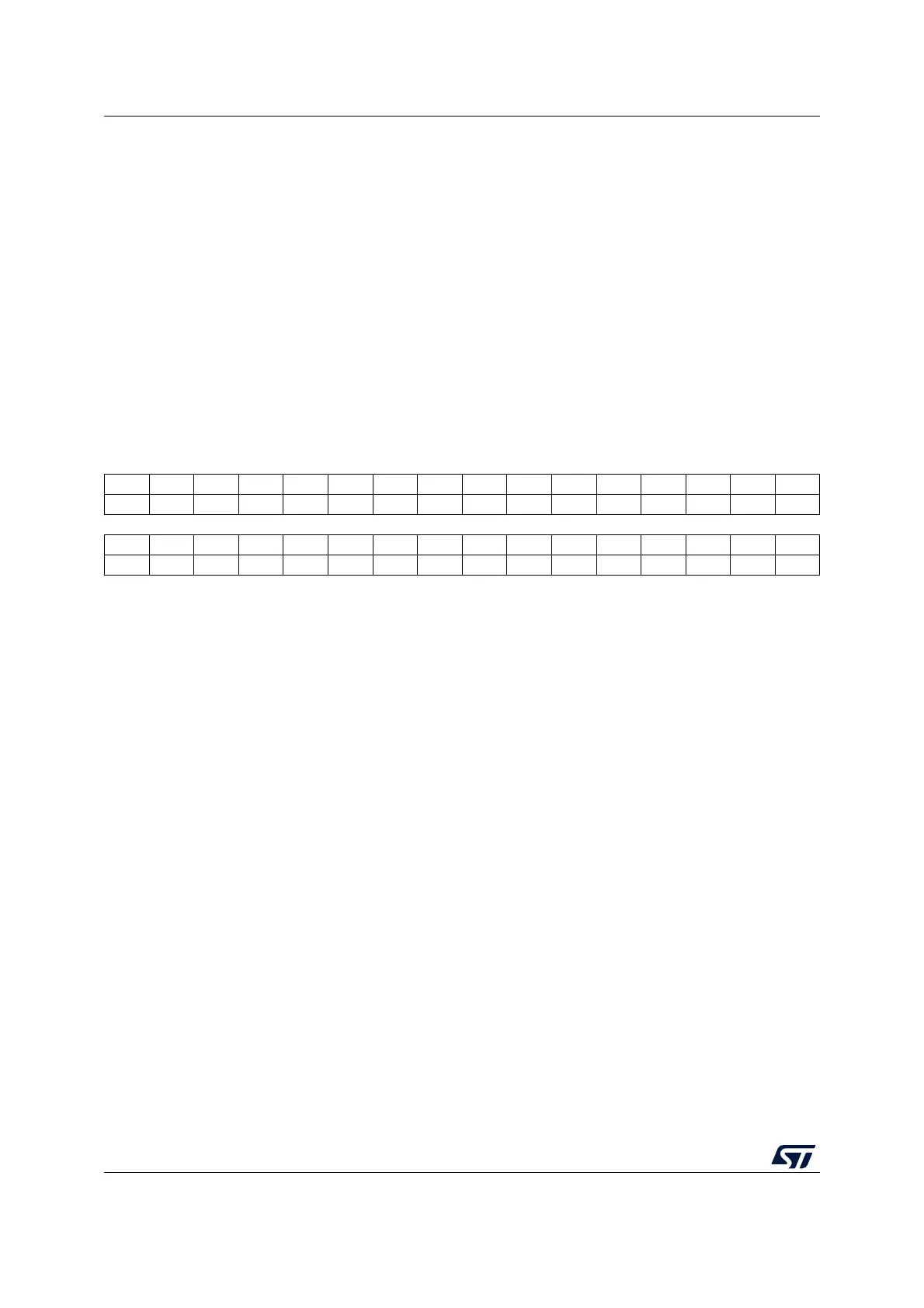

1514131211109876543210

Res. Res. SBIF CC4OF CC3OF CC2OF CC1OF B2IF BIF TIF COMIF CC4IF CC3IF CC2IF CC1IF UIF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 CC6IF: Compare 6 interrupt flag

Refer to CC1IF description (Note: Channel 6 can only be configured as output)

Bit 16 CC5IF: Compare 5 interrupt flag

Refer to CC1IF description (Note: Channel 5 can only be configured as output)

Bits 15:14 Reserved, must be kept at reset value.

Bit 13 SBIF: System Break interrupt flag

This flag is set by hardware as soon as the system break input goes active. It can be

cleared by software if the system break input is not active.

This flag must be reset to re-start PWM operation.

0: No break event occurred.

1: An active level has been detected on the system break input. An interrupt is generated if

BIE=1 in the TIMx_DIER register.

Bit 12 CC4OF: Capture/Compare 4 overcapture flag

Refer to CC1OF description

Bit 11 CC3OF: Capture/Compare 3 overcapture flag

Refer to CC1OF description

Bit 10 CC2OF: Capture/Compare 2 overcapture flag

Refer to CC1OF description

Loading...

Loading...