RM0444 Rev 5 1335/1390

RM0444 USB Type-C™ / USB Power Delivery interface (UCPD)

1346

38.7.5 UCPD interrupt mask register (UCPD_IMR)

Address offset: 0x010

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is enabled (UCPDEN = 1).

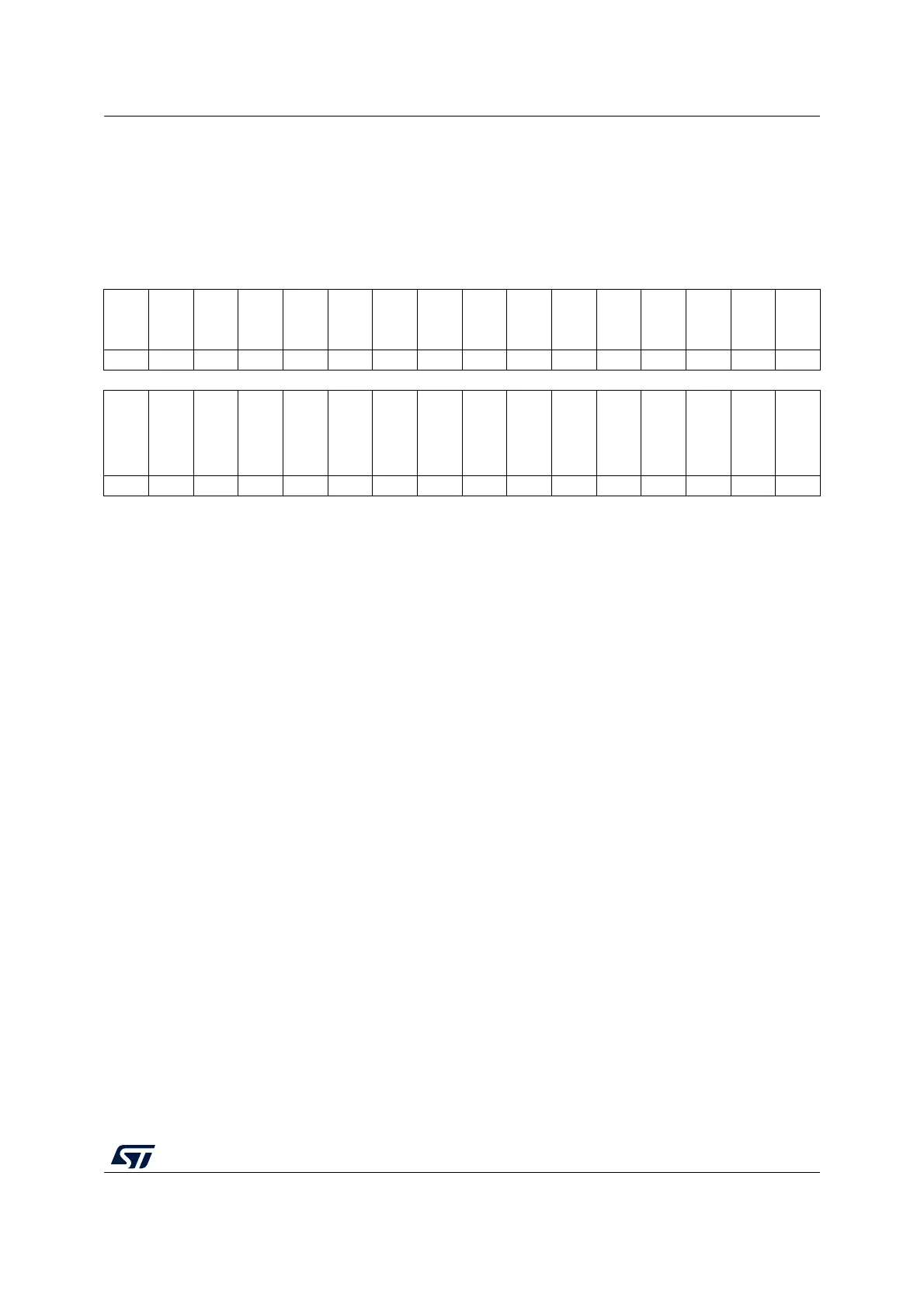

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

FRSEVTIE

Res. Res. Res. Res.

r

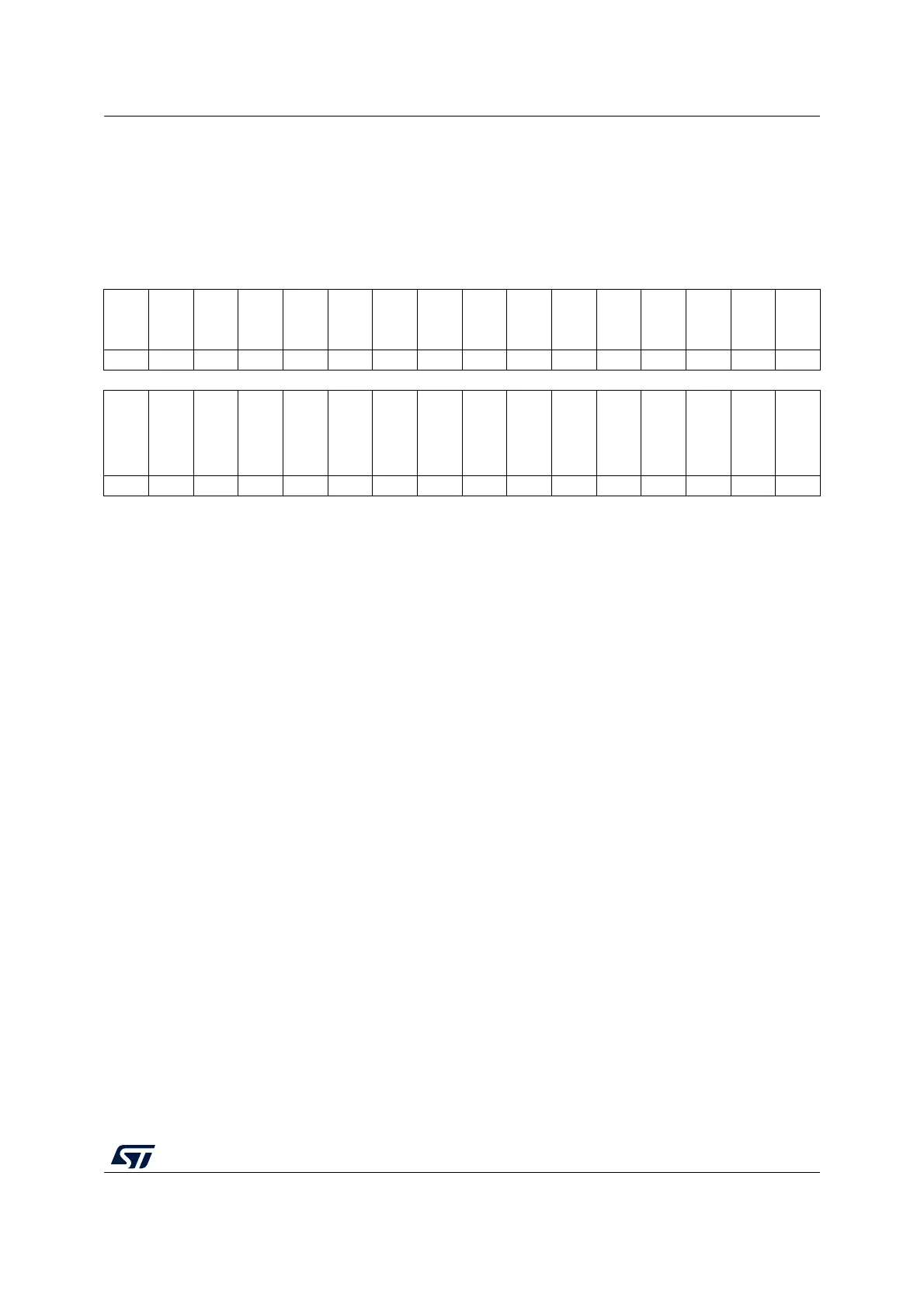

1514131211109876543210

TYPECEVT2IE

TYPECEVT1IE

Res.

RXMSGENDIE

RXOVRIE

RXHRSTDETIE

RXORDDETIE

RXNEIE

Res.

TXUNDIE

HRSTSENTIE

HRSTDISCIE

TXMSGABTIE

TXMSGSENTIE

TXMSGDISCIE

TXISIE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:21 Reserved, must be kept at reset value.

Bit 20 FRSEVTIE: FRSEVT interrupt enable

0: Disable

1: Enable

Bits 19:16 Reserved, must be kept at reset value.

Bit 15 TYPECEVT2IE: TYPECEVT2 interrupt enable

0: Disable

1: Enable

Bit 14 TYPECEVT1IE: TYPECEVT1 interrupt enable

Bit 13 Reserved, must be kept at reset value.

Bit 12 RXMSGENDIE: RXMSGEND interrupt enable

0: Disable

1: Enable

Bit 11 RXOVRIE: RXOVR interrupt enable

0: Disable

1: Enable

Bit 10 RXHRSTDETIE: RXHRSTDET interrupt enable

0: Disable

1: Enable

Bit 9 RXORDDETIE: RXORDDET interrupt enable

0: Disable

1: Enable

Bit 8 RXNEIE: RXNE interrupt enable

0: Disable

1: Enable

Bit 7 Reserved, must be kept at reset value.

Loading...

Loading...