RM0444 Rev 5 737/1390

RM0444 General-purpose timers (TIM14)

740

Note: The state of the external I/O pins connected to the standard OCx channels depends on the

OCx channel state and the GPIO registers.

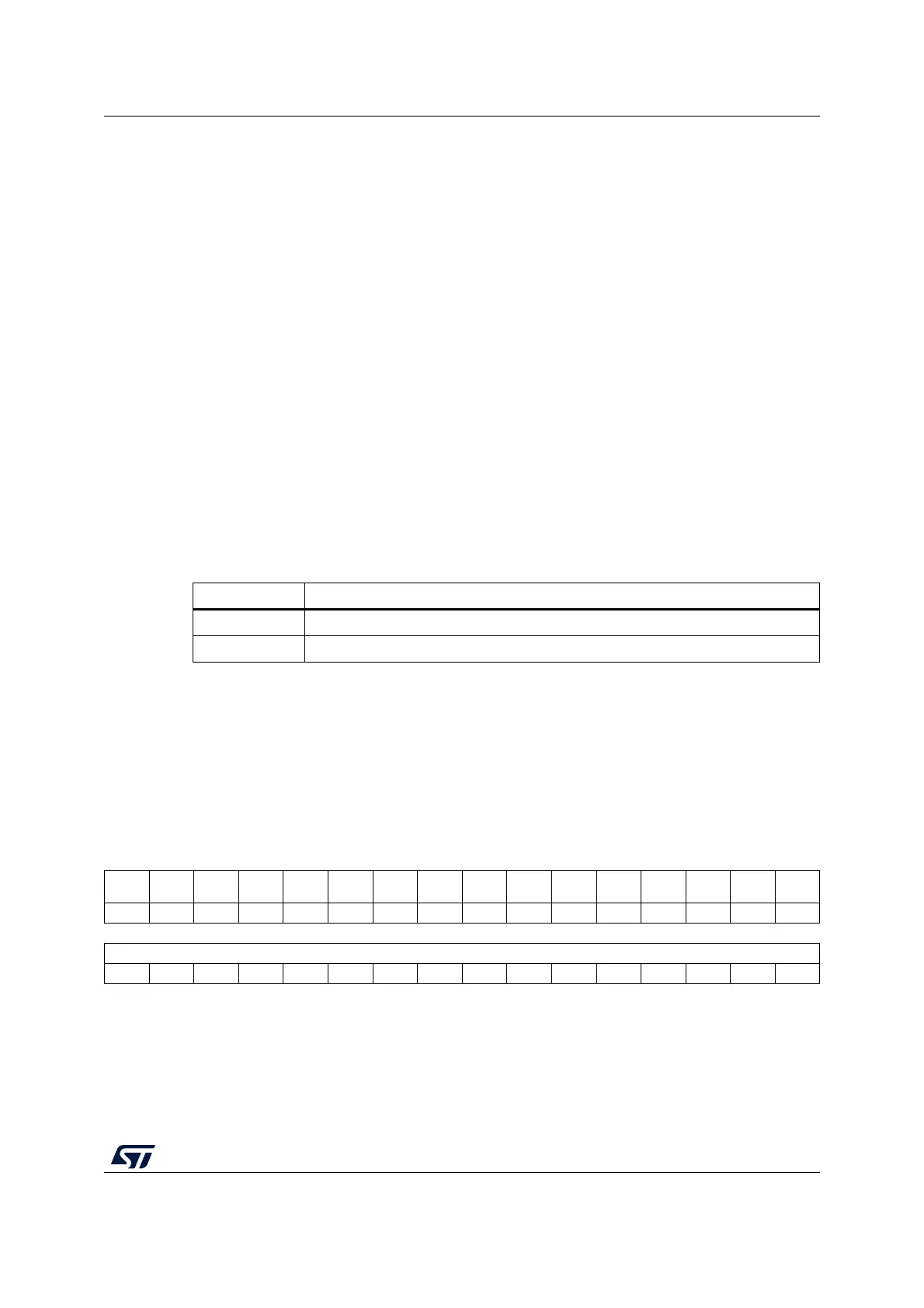

24.4.8 TIM14 counter (TIM14_CNT)

Address offset: 0x24

Reset value: 0x0000 0000

Bit 2 Reserved, must be kept at reset value.

Bit 1 CC1P: Capture/Compare 1 output Polarity.

0: OC1 active high (output mode) / Edge sensitivity selection (input mode, see below)

1: OC1 active low (output mode) / Edge sensitivity selection (input mode, see below)

When CC1 channel is configured as input, both CC1NP/CC1P bits select the active

polarity of TI1FP1 and TI2FP1 for trigger or capture operations.

CC1NP=0, CC1P=0: non-inverted/rising edge. The circuit is sensitive to TIxFP1 rising edge

(capture or trigger operations in reset, external clock or trigger mode),

TIxFP1 is not inverted (trigger operation in gated mode or encoder

mode).

CC1NP=0, CC1P=1: inverted/falling edge. The circuit is sensitive to TIxFP1 falling edge

(capture or trigger operations in reset, external clock or trigger mode),

TIxFP1 is inverted (trigger operation in gated mode or encoder mode).

CC1NP=1, CC1P=1: non-inverted/both edges/ The circuit is sensitive to both TIxFP1 rising

and falling edges (capture or trigger operations in reset, external clock

or trigger mode), TIxFP1is not inverted (trigger operation in gated

mode). This configuration must not be used in encoder mode.

CC1NP=1, CC1P=0:This configuration is reserved, it must not be used.

Bit 0 CC1E: Capture/Compare 1 output enable.

0: Capture mode disabled / OC1 is not active

1: Capture mode enabled / OC1 signal is output on the corresponding output pin

Table 123. Output control bit for standard OCx channels

CCxE bit OCx output state

0 Output disabled (not driven by the timer: Hi-Z)

1 Output enabled (tim_ocx = tim_ocxref + Polarity)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

UIF

CPY

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

1514131211109876543210

CNT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 UIFCPY: UIF Copy

This bit is a read-only copy of the UIF bit in the TIMx_ISR register.

Bits 30:16 Reserved, must be kept at reset value.

Bits 15:0 CNT[15:0]: Counter value

Loading...

Loading...