Extended interrupt and event controller (EXTI) RM0444

330/1390 RM0444 Rev 5

Reset value: 0x0000 0000

Contains only register bits for configurable events.

13.5.10 EXTI falling edge pending register 2 (EXTI_FPR2)

Address offset: 0x038

Reset value: 0x0000 0000

Contains only register bits for configurable events.

13.5.11 EXTI external interrupt selection register (EXTI_EXTICRx)

Address offset: 0x060 + 0x4 * (x - 1), (x = 1 to 4)

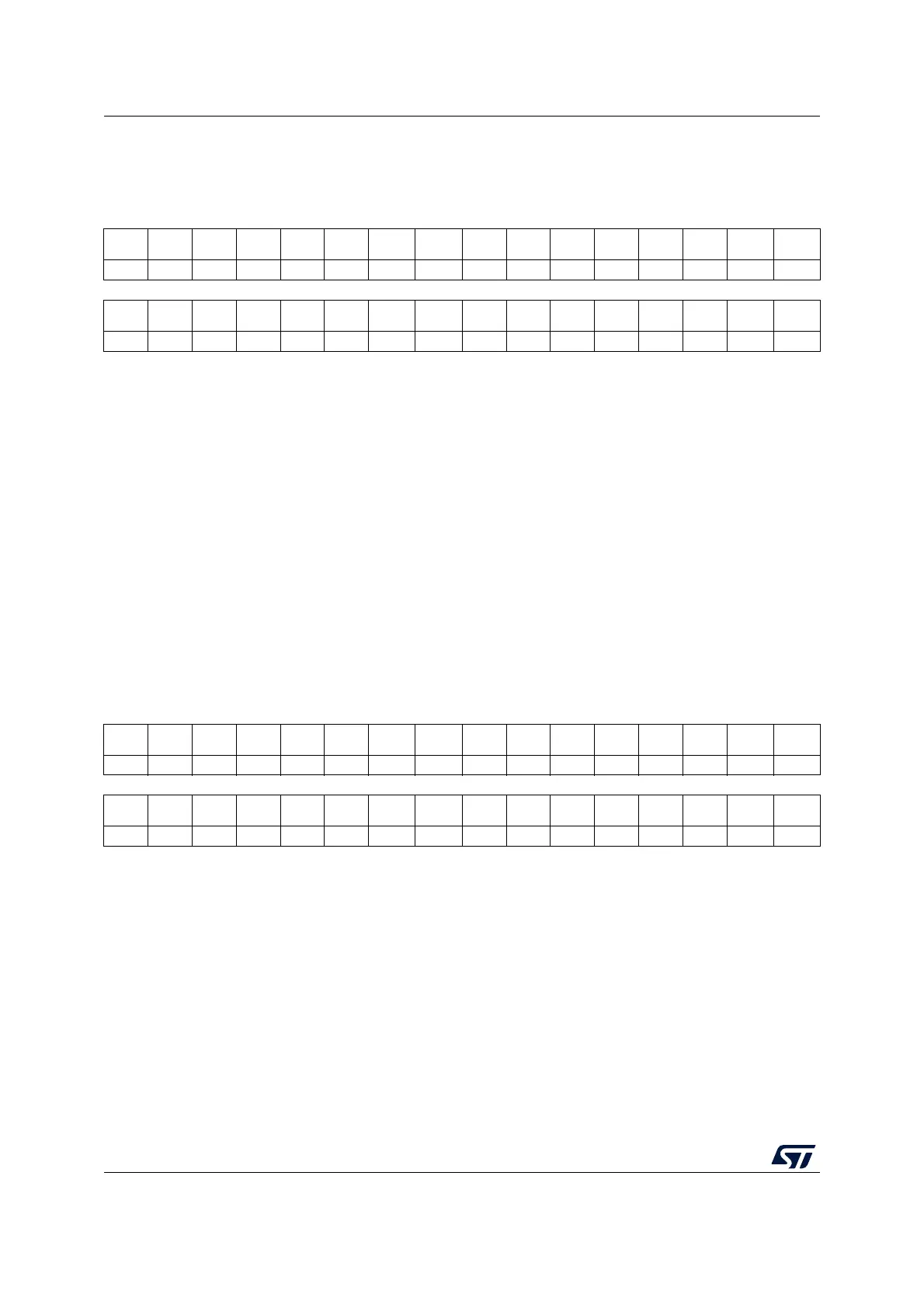

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 7654321 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RPIF2 Res. Res.

rc_w1

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 RPIF2: Rising edge event pending for configurable line 34

This bit is set upon a rising edge event generated by hardware or by software (through the

EXTI_SWIER2 register) on line 34. This bit is cleared by writing 1 into it.

0: No rising edge trigger request occurred

1: Rising edge trigger request occurred

The RPIF2 bit is only available in STM32G0B1xx and STM32G0C1xx. This bit is reserved in

all the other devices.

Bits 1:0 Reserved, must be kept at reset value.

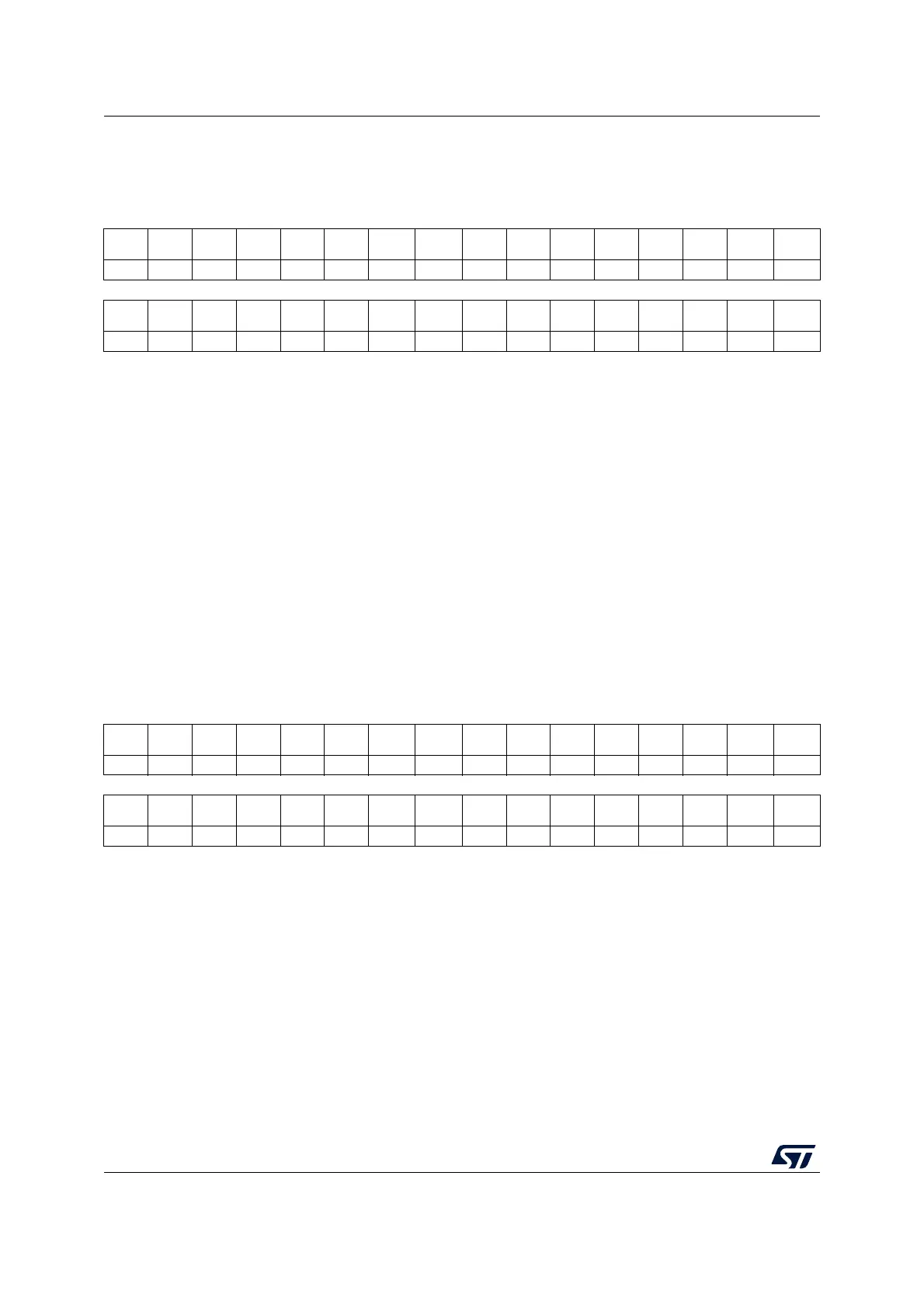

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 7654321 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. FPIF2 Res. Res.

rc_w1

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 FPIF2: Falling edge event pending for configurable line 34

This bit is set upon a falling edge event generated by hardware or by software (through the

EXTI_SWIER2 register) on the line 34. This bit is cleared by writing 1 into it.

0: No falling edge trigger request occurred

1: Falling edge trigger request occurred

The FPIF2 bit is only available in STM32G0B1xx and STM32G0C1xx. This bit is reserved in

all the other devices.

Bits 1:0 Reserved, must be kept at reset value.

Loading...

Loading...