RM0444 Rev 5 925/1390

RM0444 Tamper and backup registers (TAMP)

926

31.6.8 TAMP backup x register (TAMP_BKPxR)

Address offset: 0x100 + 0x04 * x, (x = 0 to 4)

Backup domain reset value: 0x0000 0000

System reset: not affected

Bit 17 Reserved, must be kept at reset value.

Bit 16 Reserved, must be kept at reset value.

Bits 15:3 Reserved, must be kept at reset value.

Bit 2 CTAMP3F: Clear TAMP3 detection flag

Writing 1 in this bit clears the TAMP3F bit in the TAMP_SR register.

Bit 1 CTAMP2F: Clear TAMP2 detection flag

Writing 1 in this bit clears the TAMP2F bit in the TAMP_SR register.

Bit 0 CTAMP1F: Clear TAMP1 detection flag

Writing 1 in this bit clears the TAMP1F bit in the TAMP_SR register.

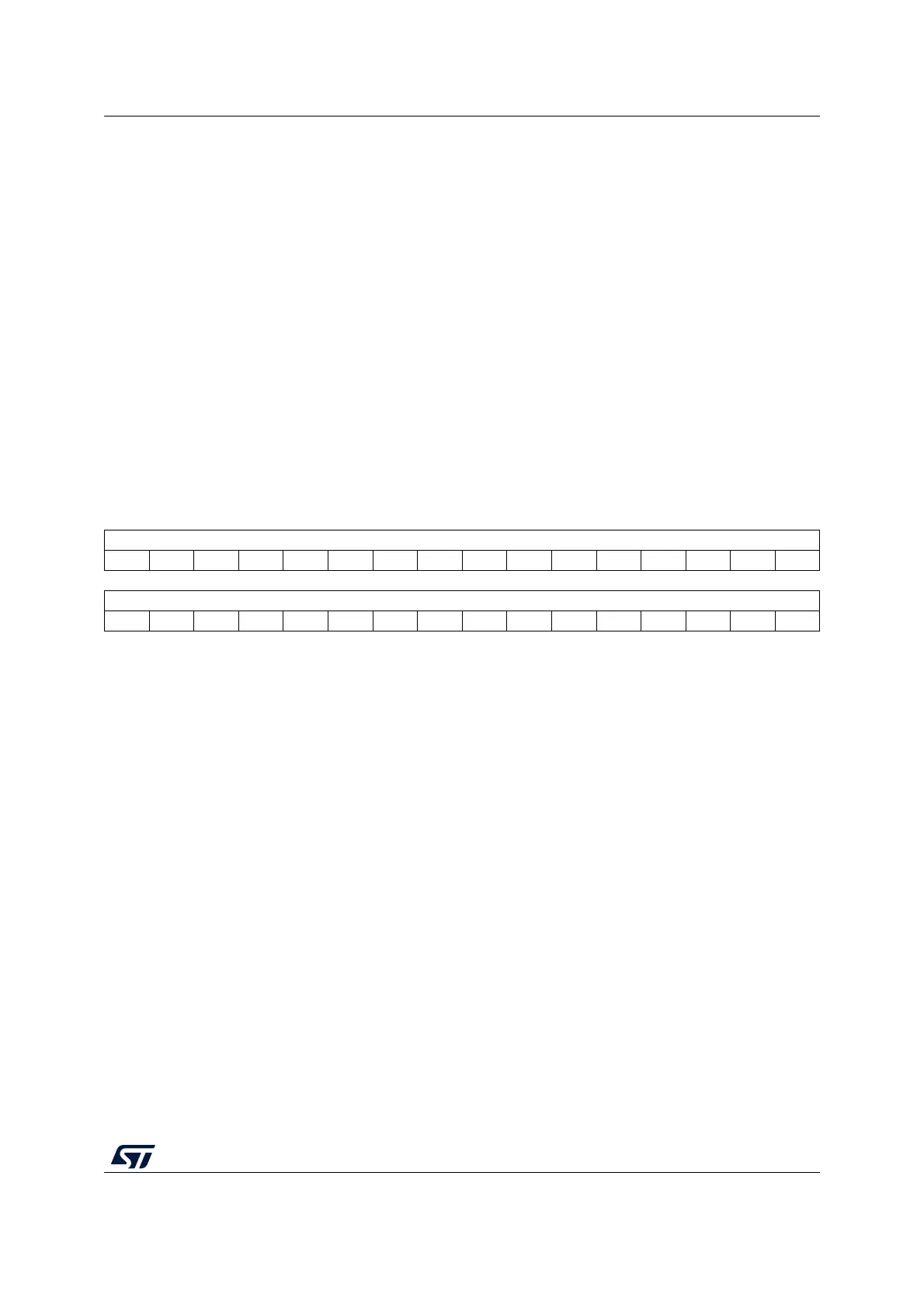

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

BKP[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

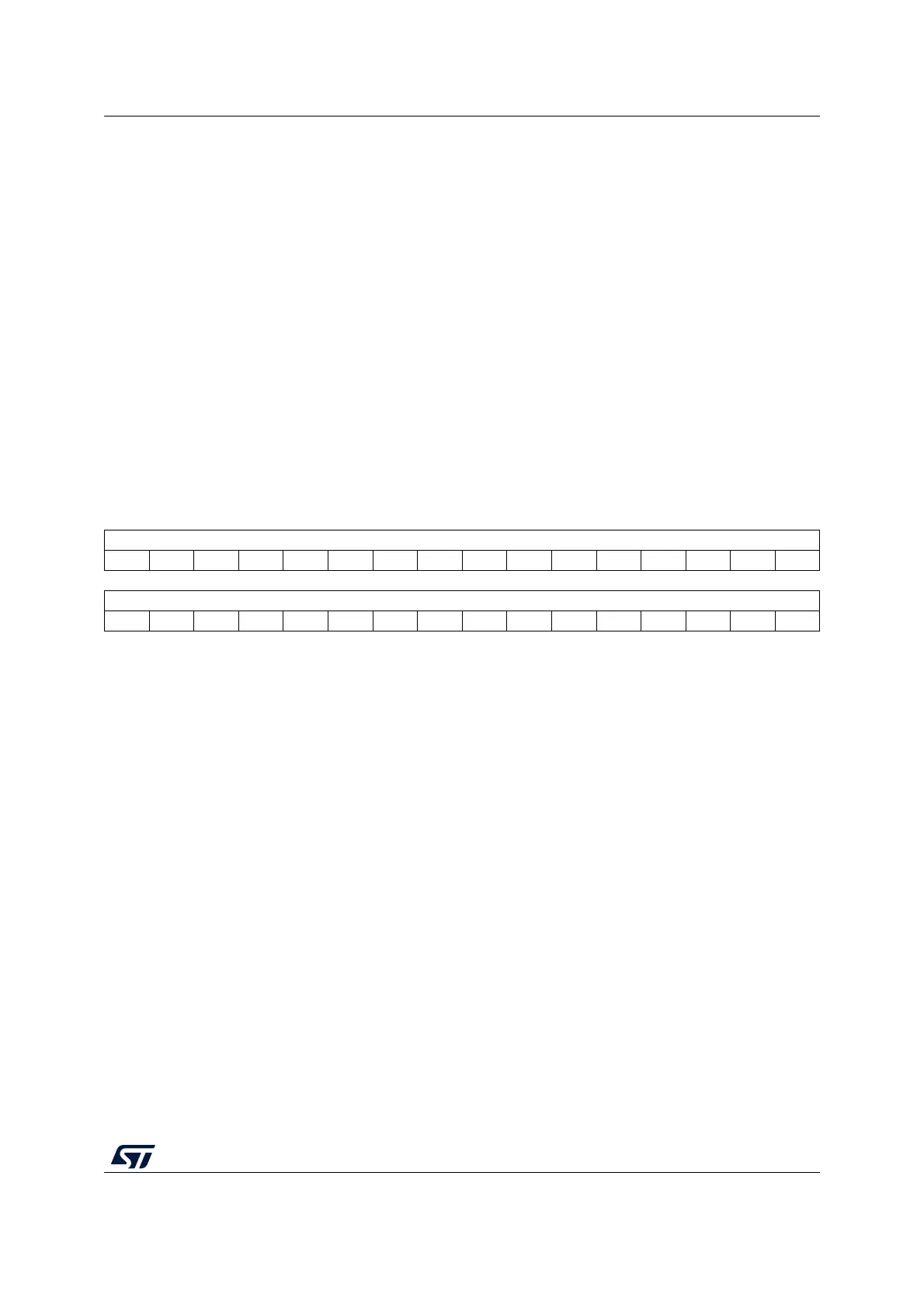

1514131211109876543210

BKP[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw w rw rw

Bits 31:0 BKP[31:0]

The application can write or read data to and from these registers.

They are powered-on by V

BAT

when V

DD

is switched off, so that they are not reset by System

reset, and their contents remain valid when the device operates in low-power mode.

In the default configuration this register is reset on a tamper detection event. It is forced to

reset value as long as there is at least one internal or external tamper flag being set. This

register is also reset when the readout protection (RDP) is disabled.

Loading...

Loading...