Low-power timer (LPTIM) RM0444

854/1390 RM0444 Rev 5

26.7.9 LPTIM configuration register 2 (LPTIM_CFGR2)

Address offset: 0x024

Reset value: 0x0000 0000

Caution: The LPTIM_CFGR2 register must only be modified when the LPTIM is disabled (ENABLE

bit reset to ‘0’).

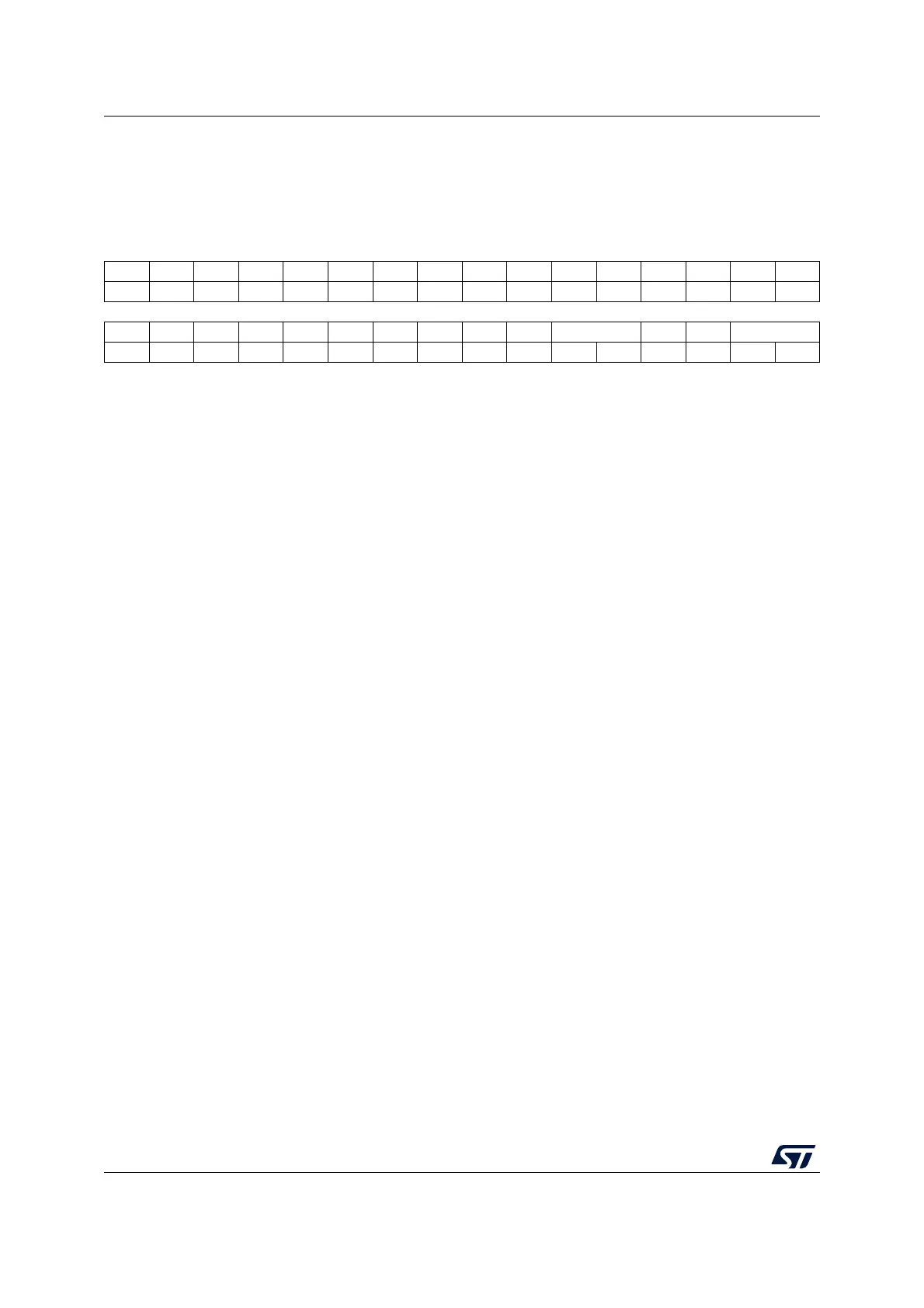

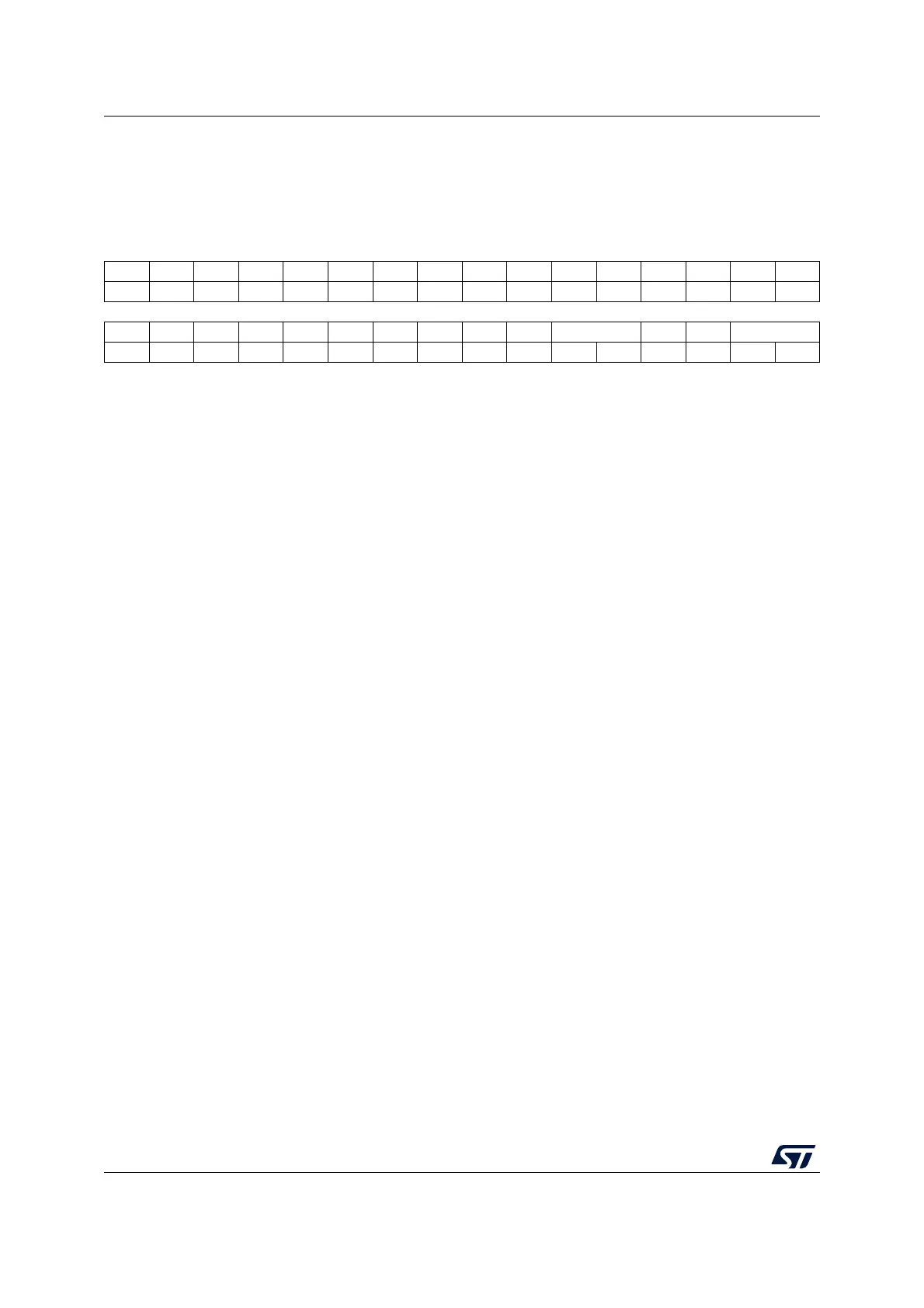

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. IN2SEL[1:0] Res. Res. IN1SEL[1:0]

rw rw rw rw

Bits 31:6 Reserved, must be kept at reset value.

Bits 5:4 IN2SEL[1:0]: LPTIM input 2 selection

The IN2SEL bits control the LPTIM Input 2 multiplexer, which connect LPTIM Input 2 to one of the

available inputs.

00: lptim_in2_mux0

01: lptim_in2_mux1

10: lptim_in2_mux2

11: lptim_in2_mux3

For connection details refer to Section 26.4.3: LPTIM input and trigger mapping.

Note: If the LPTIM does not support encoder mode feature, these bits are reserved. Please refer to

Section 26.3: LPTIM implementation.

Bits 3:2 Reserved, must be kept at reset value.

Bits 1:0 IN1SEL[1:0]: LPTIM input 1 selection

The IN1SEL bits control the LPTIM Input 1 multiplexer, which connects LPTIM Input 1 to one of the

available inputs.

00: lptim_in1_mux0

01: lptim_in1_mux1

10: lptim_in1_mux2

11: lptim_in1_mux3

For connection details refer to Section 26.4.3: LPTIM input and trigger mapping.

Loading...

Loading...