Embedded Flash memory (FLASH) RM0444

80/1390 RM0444 Rev 5

The word write operation is completed when the corresponding busy flag (BSY1 or BSY2) is

back to low. The EOP interrupt can be used to indicate that event to the application

software.

3.4 FLASH option bytes

3.4.1 FLASH option byte description

The option bytes are configured by the end user depending on the application requirements.

As a configuration example, the watchdog may be selected in hardware or software mode

(refer to Section 3.4.2: FLASH option byte programming).

A double word is split up in option bytes as indicated in Table 15.

The organization of these bytes in the information block is shown in Table 16 (superset for

single-bank and dual-bank devices). The option bytes can be read from the Flash memory

locations listed in Table 16 or from the Option byte registers:

• FLASH option register (FLASH_OPTR)

• FLASH PCROP area A start address register (FLASH_PCROP1ASR)

• FLASH PCROP area A end address register (FLASH_PCROP1AER)

• FLASH PCROP area B start address register (FLASH_PCROP1BSR)

• FLASH PCROP area B end address register (FLASH_PCROP1BER)

• FLASH PCROP2 area A start address register (FLASH_PCROP2ASR)

• FLASH PCROP2 area A end address register (FLASH_PCROP2AER)

• FLASH PCROP2 area B start address register (FLASH_PCROP2BSR)

• FLASH PCROP2 area B end address register (FLASH_PCROP2BER)

• FLASH WRP area A address register (FLASH_WRP1AR)

• FLASH WRP area B address register (FLASH_WRP1BR)

• FLASH WRP2 area A address register (FLASH_WRP2AR)

• FLASH WRP2 area B address register (FLASH_WRP2BR)

• FLASH security register (FLASH_SECR)

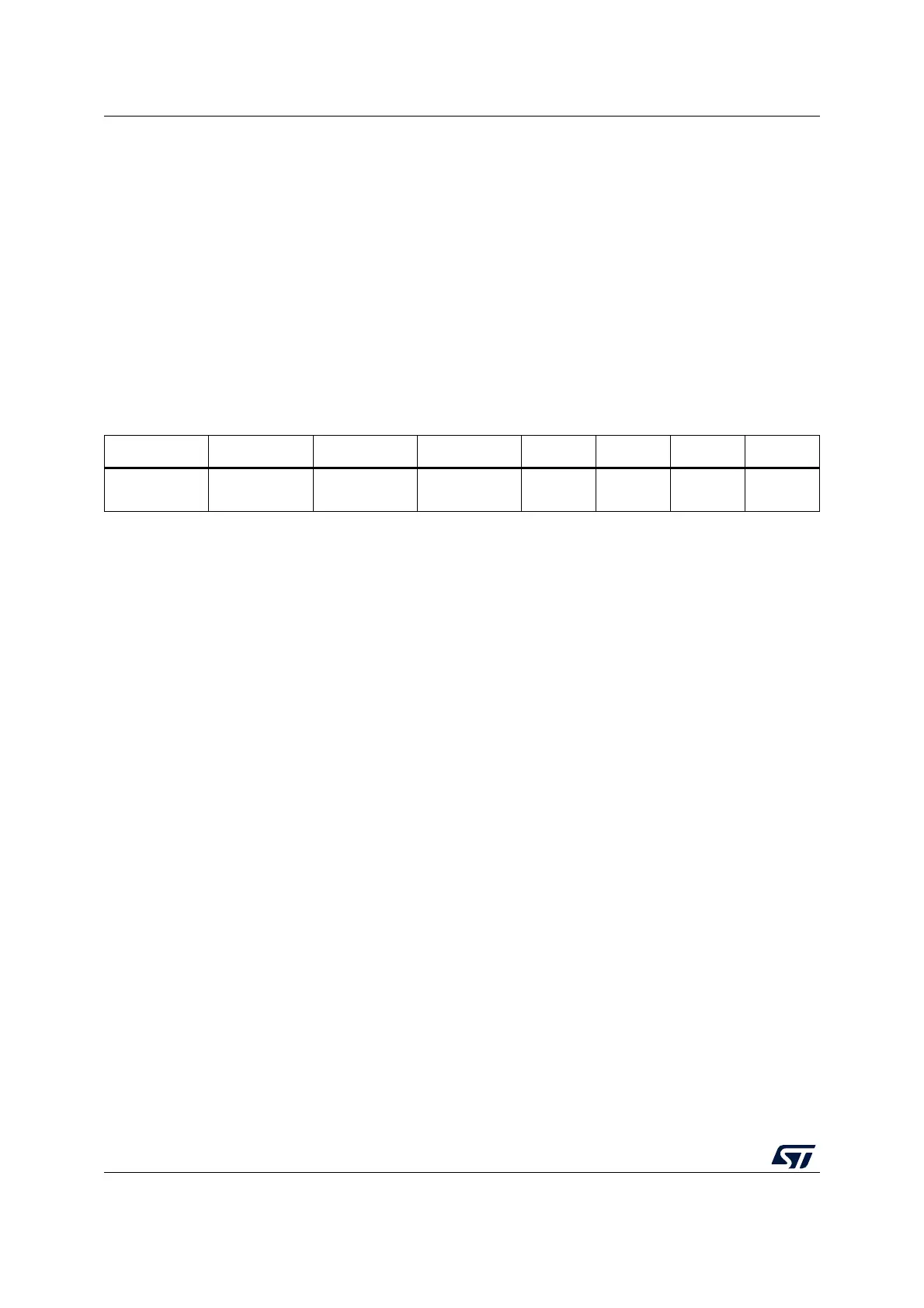

Table 15. Option byte format

63-56 55-48 47-40 39-32 31-24 23-16 15 -8 7-0

Complemented

option byte 3

Complemented

option byte 2

Complemented

option byte 1

Complemented

option byte 0

Option

byte 3

Option

byte 2

Option

byte 1

Option

byte 0

Loading...

Loading...