RM0444 Rev 5 251/1390

RM0444 System configuration controller (SYSCFG)

269

8.1.2 SYSCFG configuration register 2 (SYSCFG_CFGR2)

Address offset: 0x18

System reset value: 0x0000 0000

Bit 5 IR_POL: IR output polarity selection

0: Output of IRTIM (IR_OUT) is not inverted

1: Output of IRTIM (IR_OUT) is inverted

Bit 4 PA12_RMP: PA12 pin remapping

This bit is set and cleared by software. When set, it remaps the PA12 pin to operate as PA10

GPIO port, instead as PA12 GPIO port.

0: No remap (PA12)

1: Remap (PA10)

Bit 3 PA11_RMP: PA11 pin remapping

This bit is set and cleared by software. When set, it remaps the PA11 pin to operate as PA9

GPIO port, instead as PA11 GPIO port.

0: No remap (PA11)

1: Remap (PA9)

Bit 2 Reserved, must be kept at reset value.

Bits 1:0 MEM_MODE[1:0]: Memory mapping selection bits

These bits are set and cleared by software. They control the memory internal mapping at

address 0x0000 0000. After reset these bits take on the value selected by the actual boot

mode configuration. Refer to Section 2.5: Boot configuration for more details.

x0: Main Flash memory mapped at 0x0000 0000

01: System Flash memory mapped at 0x0000 0000

11: Embedded SRAM mapped at 0x0000 0000

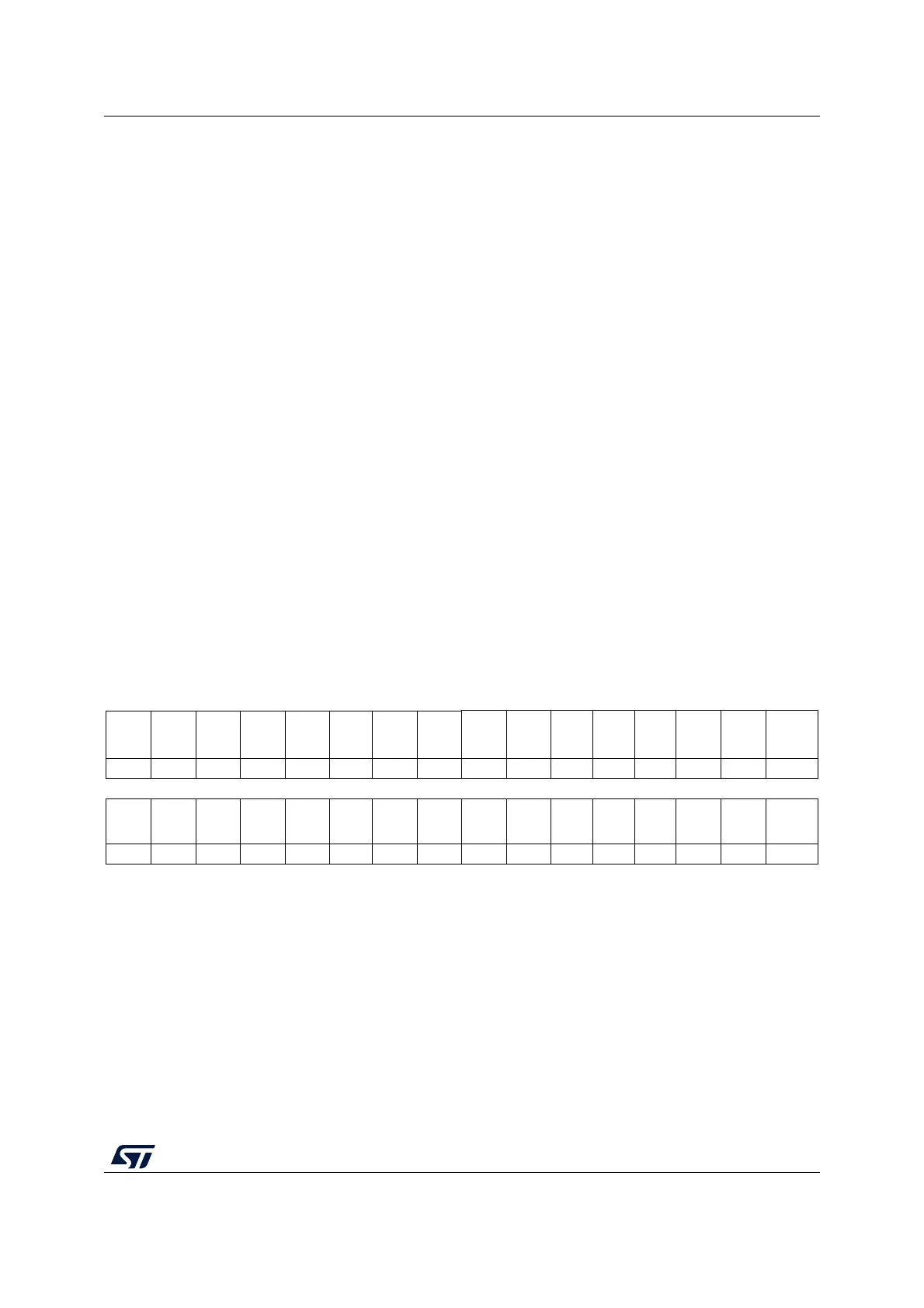

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res.

PB2_

CDEN

(1)

PB1_

CDEN

(1)

PB0_

CDEN

(1)

PA13_

CDEN

(1)

PA6_

CDEN

(1)

PA5_

CDEN

(1)

PA3_

CDEN

(1)

PA1_

CDEN

(1)

rw rw rw rw rw rw rw rw

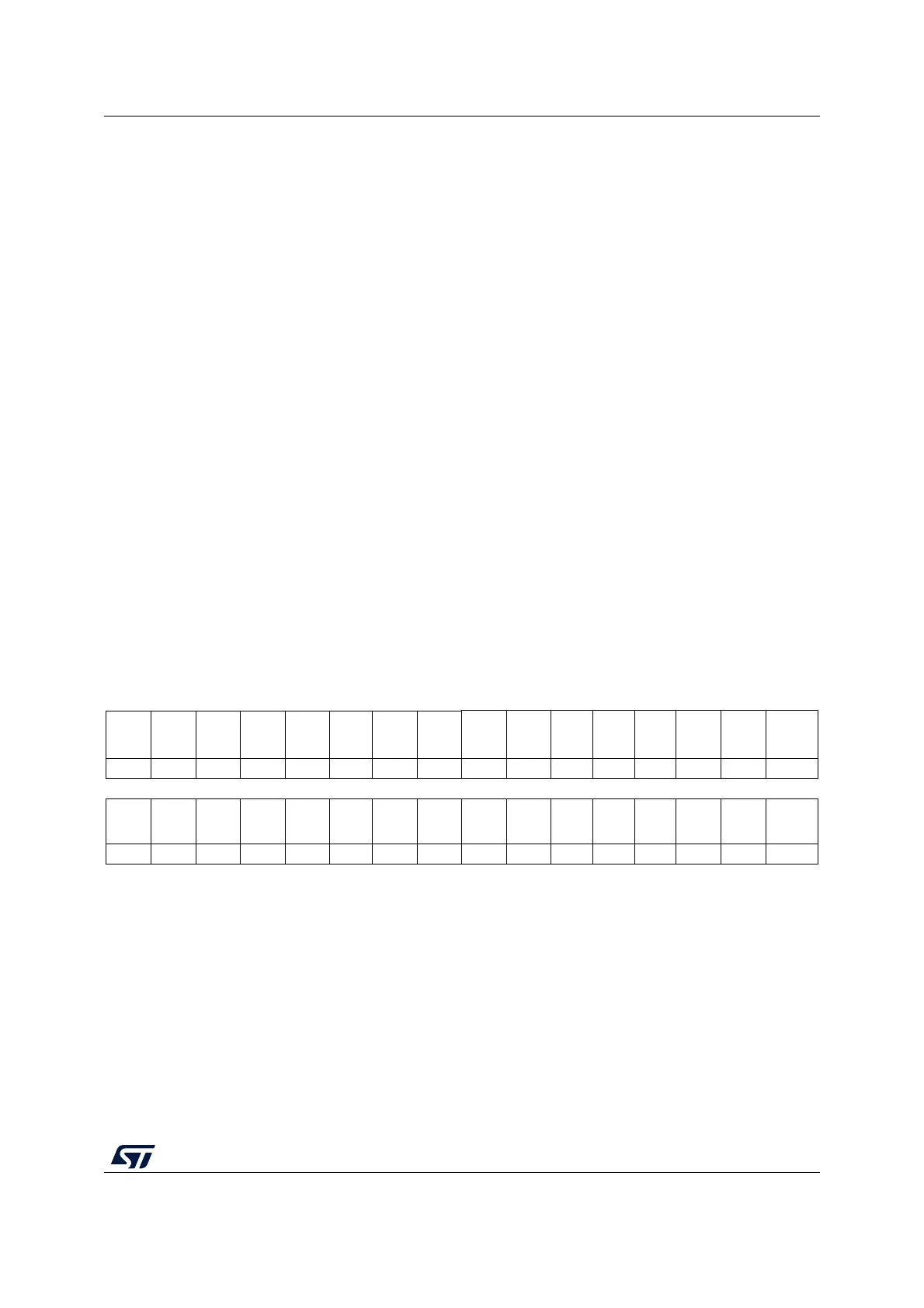

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res.

SRAM_

PEF

Res. Res. Res. Res.

ECC_

LOCK

PVD_

LOCK

SRAM_

PARITY

_LOCK

LOCKUP

_LOCK

rc_w1 rw rw rw rw

1. Only significant on devices integrating switchable clamping diodes, otherwise reserved. Refer to Section 1.4: Availability of

peripherals.

Loading...

Loading...