RM0444 Rev 5 135/1390

RM0444 Power control (PWR)

159

4.3.6 Stop 0 mode

The Stop 0 mode is based on the Cortex

®

-M0+ deepsleep mode combined with the

peripheral clock gating. The voltage regulator is configured in main regulator mode. In Stop

0 mode, all clocks in the V

CORE

domain are stopped; the PLL, the HSI16 and the HSE

oscillators are disabled. Some peripherals with the wakeup capability (I2C1, USART1,

USART2, and LPUART1) can switch on the HSI16 to receive a frame, and switch off the

HSI16 after receiving the frame if it is not a wakeup frame. In this case, the HSI16 clock is

propagated only to the peripheral requesting it.

SRAM and register contents are preserved.

The BOR is available in Stop 0 mode.

The BOR and PDR can be activated to sample periodically the supply voltage. This option

enabled by setting the ENB_ULP bit of the PWR_CR3 register allows decreasing the

current consumption in this mode, but any drop of the voltage below the operating

conditions between two active periods of the supply detector results in a non-generation of

PDR reset.

I/O states in Stop 0 mode

In the Stop 0 mode, all I/O pins keep the same state as in the Run mode.

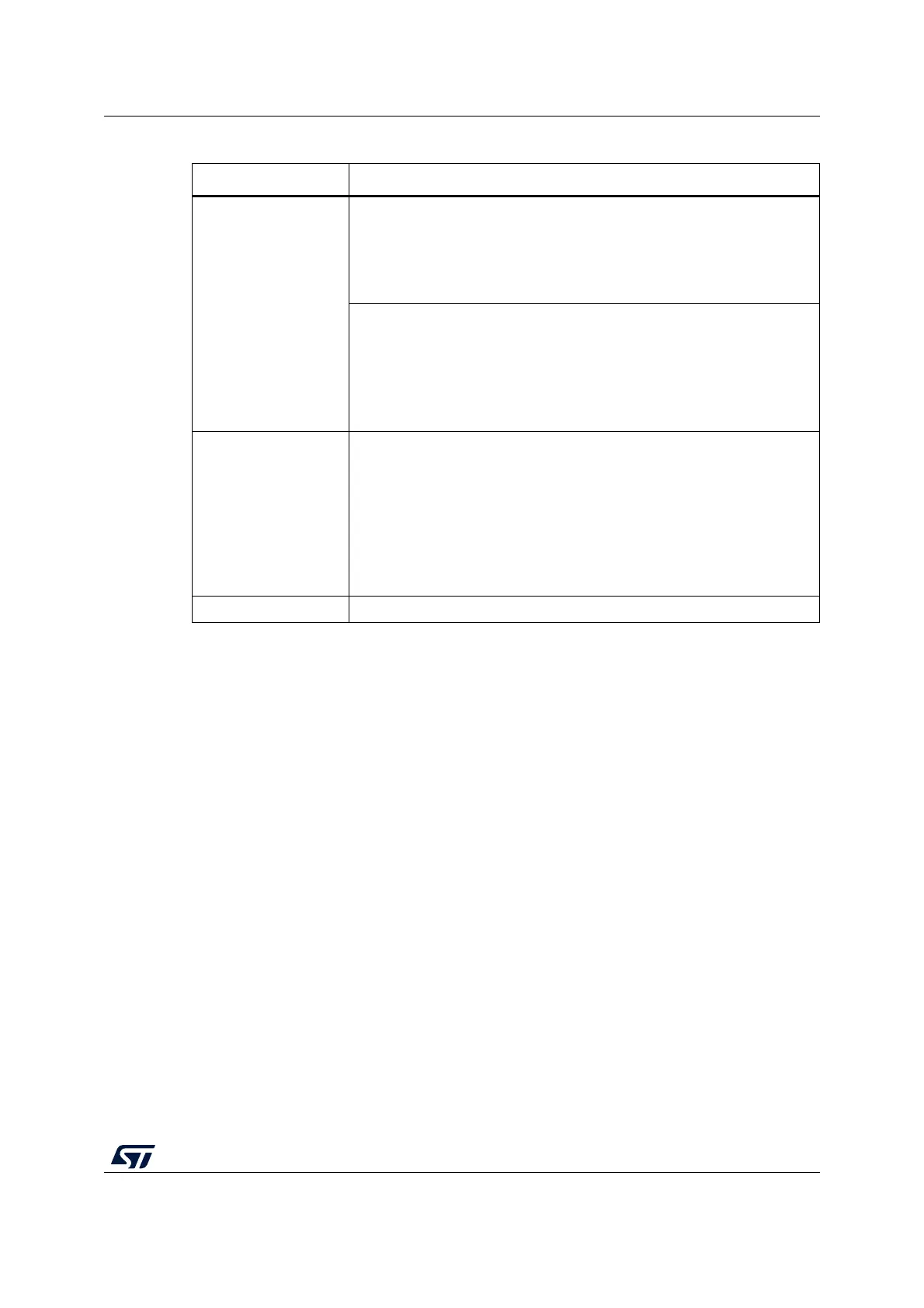

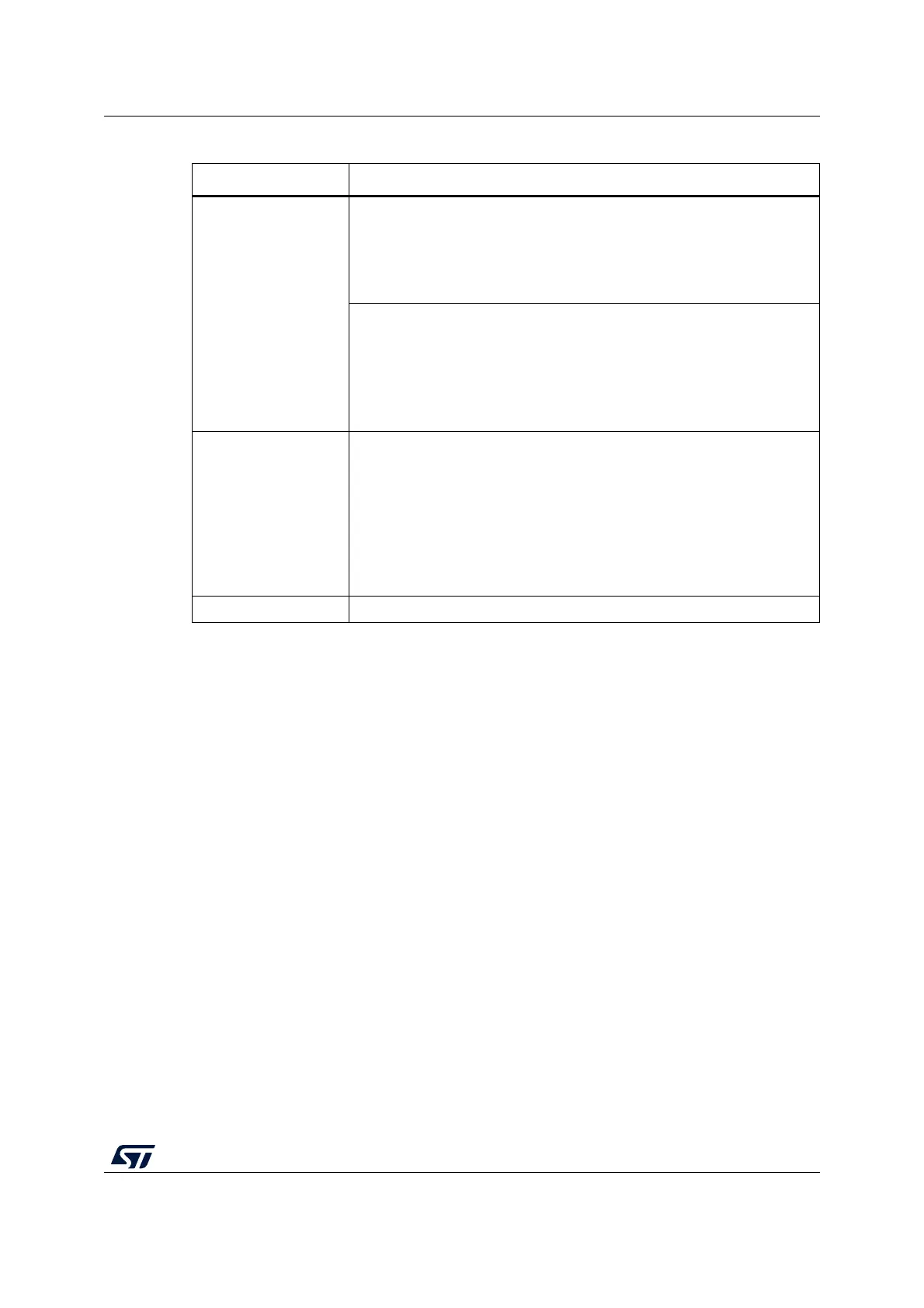

Table 29. Low-power sleep mode summary

Characteristic Description

Mode entry

Low-power sleep mode is entered from the Low-power run mode.

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0

– No interrupt (for WFI) or event (for WFE) is pending

Refer to the Cortex

®

-M0+ System Control register.

Low-power sleep mode is entered from the Low-power run mode.

On return from ISR while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 1

– No interrupt is pending

Refer to the Cortex

®

-M0+ System Control register.

Mode exit

If WFI or Return from ISR was used for entry

Interrupt: refer to Table 58: Vector table

If WFE was used for entry and SEVONPEND = 0:

Wakeup event: refer to Section 13.3.2: EXTI direct event input wakeup

If WFE was used for entry and SEVONPEND = 1:

Interrupt even when disabled in NVIC: refer to Table 58: Vector table

Wakeup event: refer to Section 13.3.2: EXTI direct event input wakeup

After exiting Low-power sleep mode, the MCU is in Low-power run mode.

Wakeup latency None

Loading...

Loading...