RM0444 Rev 5 65/1391

RM0444

68

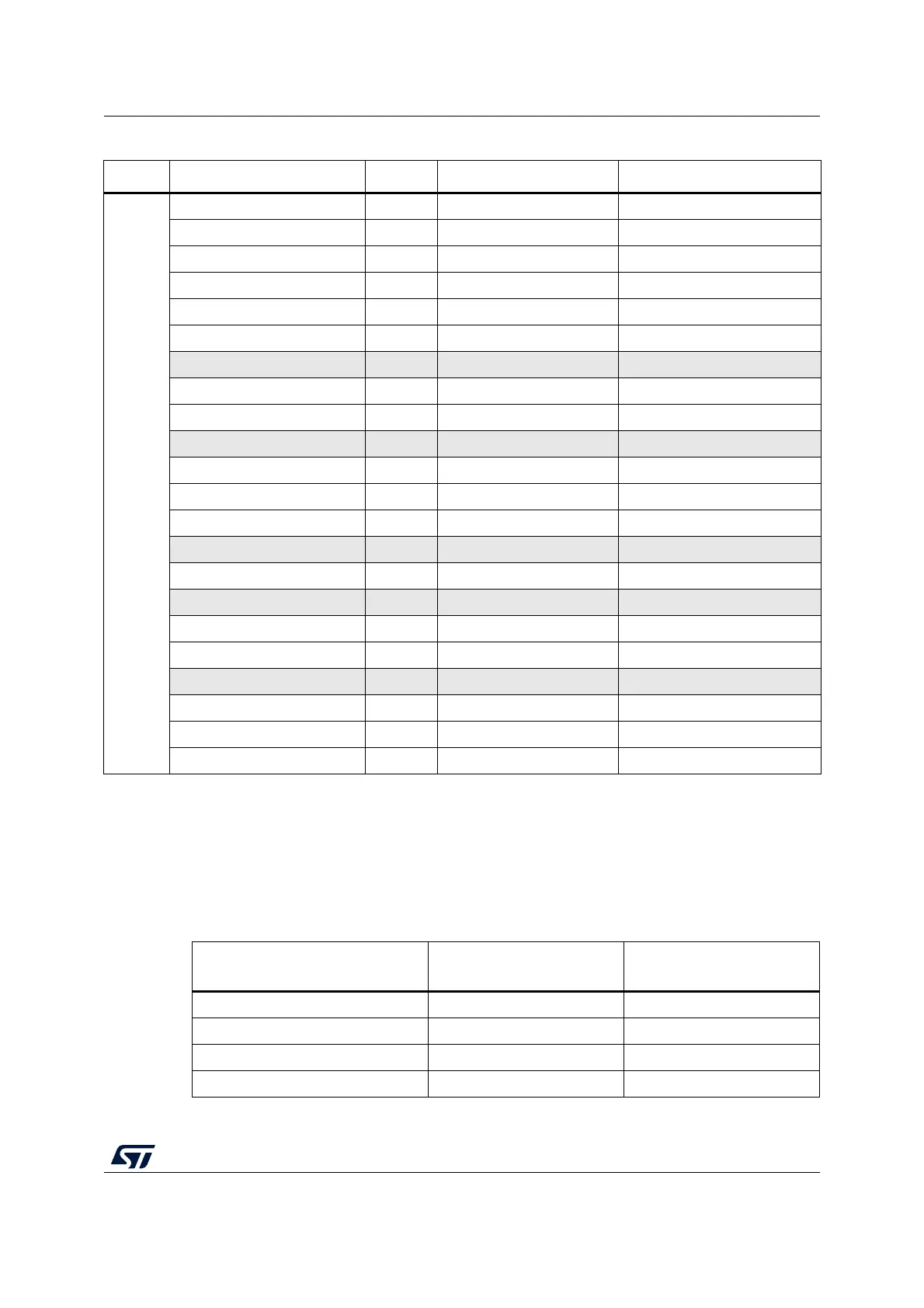

2.3 Embedded SRAM

The following table summarizes the SRAM resources on the devices, with parity check

enabled and disabled.

.

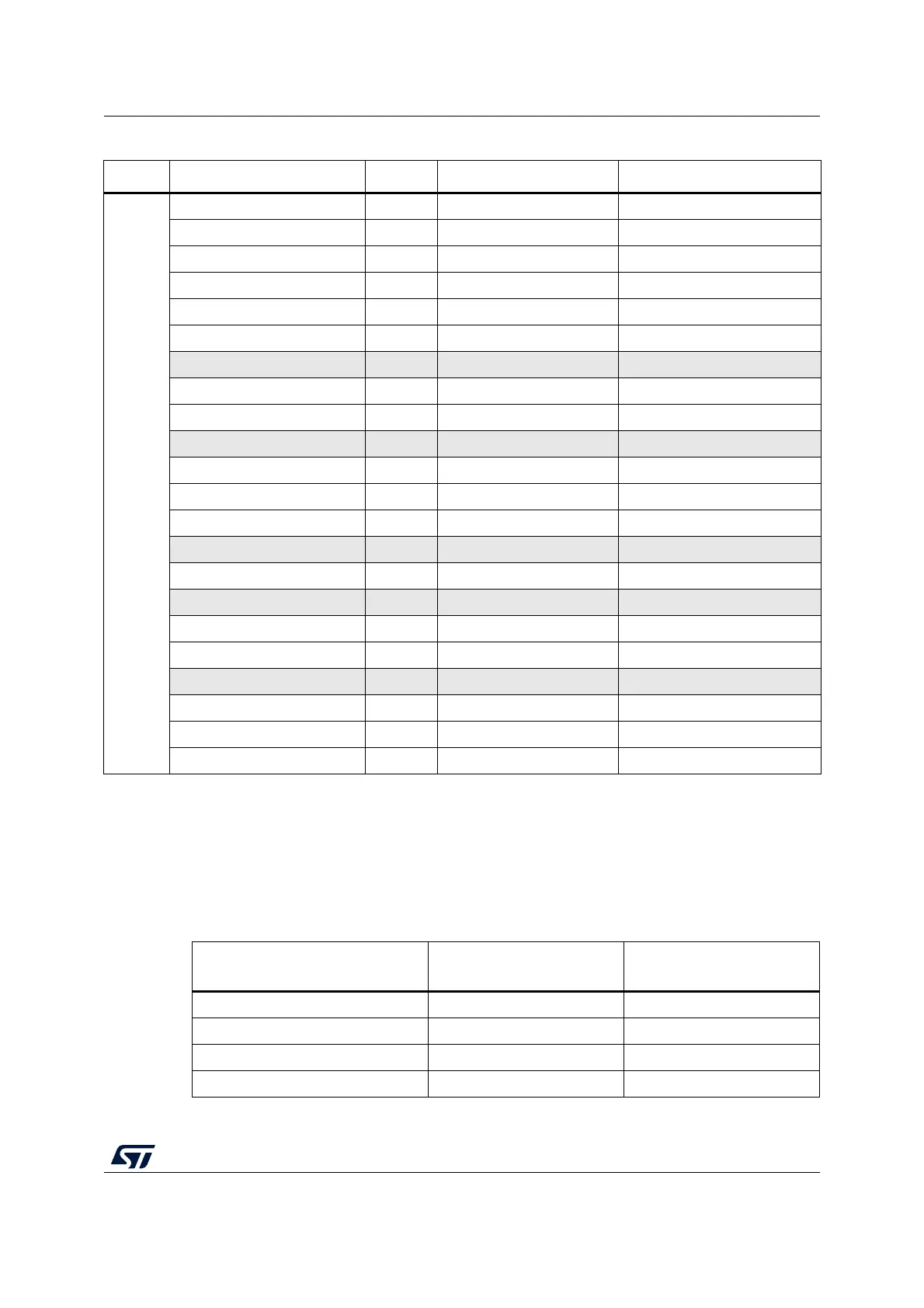

APB

0x4000 5800 - 0x4000 5BFF 1 KB I2C2 Section 32.7.12 on page 998

0x4000 5400 - 0x4000 57FF 1 KB I2C1 Section 32.7.12 on page 998

0x4000 5000 - 0x4000 53FF 1 KB USART5 Section 33.8.15 on page 1086

0x4000 4C00 - 0x4000 4FFF 1 KB USART4 Section 33.8.15 on page 1086

0x4000 4800 - 0x4000 4BFF 1 KB USART3 Section 33.8.15 on page 1086

0x4000 4400 - 0x4000 47FF 1 KB USART2 Section 33.8.15 on page 1086

0x4000 4000 - 0x4000 43FF 1KB Reserved -

0x4000 3C00 - 0x4000 3FFF 1 KB SPI3 Section 35.9.10 on page 1197

0x4000 3800 - 0x4000 3BFF 1 KB SPI2/I2S2 Section 35.9.10 on page 1197

0x4000 3400 - 0x4000 37FF 1KB Reserved -

0x4000 3000 - 0x4000 33FF 1 KB IWDG Section 28.4.6 on page 868

0x4000 2C00 - 0x4000 2FFF 1 KB WWDG Section 29.5.4 on page 874

0x4000 2800 - 0x4000 2BFF 1 KB RTC Section 30.6.21 on page 912

0x4000 2400 - 0x4000 27FF 1KB Reserved -

0x4000 2000 - 0x4000 23FF 1 KB TIM14 Section 24.4.13 on page 740

0x4000 1800 - 0x4000 1FFF 2KB Reserved -

0x4000 1400 - 0x4000 17FF 1 KB TIM7 Section 23.4.9 on page 715

0x4000 1000 - 0x4000 13FF 1 KB TIM6 Section 23.4.9 on page 715

0x4000 0C00 - 0x4000 0FFF 1KB Reserved -

0x4000 0800 - 0x4000 0BFF 1 KB TIM4 Section 22.4.31 on page 700

0x4000 0400 - 0x4000 07FF 1 KB TIM3 Section 22.4.31 on page 700

0x4000 0000 - 0x4000 03FF 1 KB TIM2 Section 22.4.31 on page 700

1. SYSCFG (ITLINE) registers use 0x4001 0000 as reference peripheral base address.

Table 6. STM32G0x1 peripheral register boundary addresses (continued)

Bus Boundary address Size Peripheral Peripheral register map

Table 7. SRAM size

Device

SRAM with parity enabled

(Kbyte)

SRAM with parity disabled

(Kbyte)

STM32G0B1xx and STM32G0C1xx 128 144

STM32G071xx and STM32G081xx 32 36

STM32G051xx and STM32G061xx 16 18

STM32G031xx and STM32G041xx 8 8

Loading...

Loading...