RM0444 Rev 5 203/1390

RM0444 Reset and clock control (RCC)

220

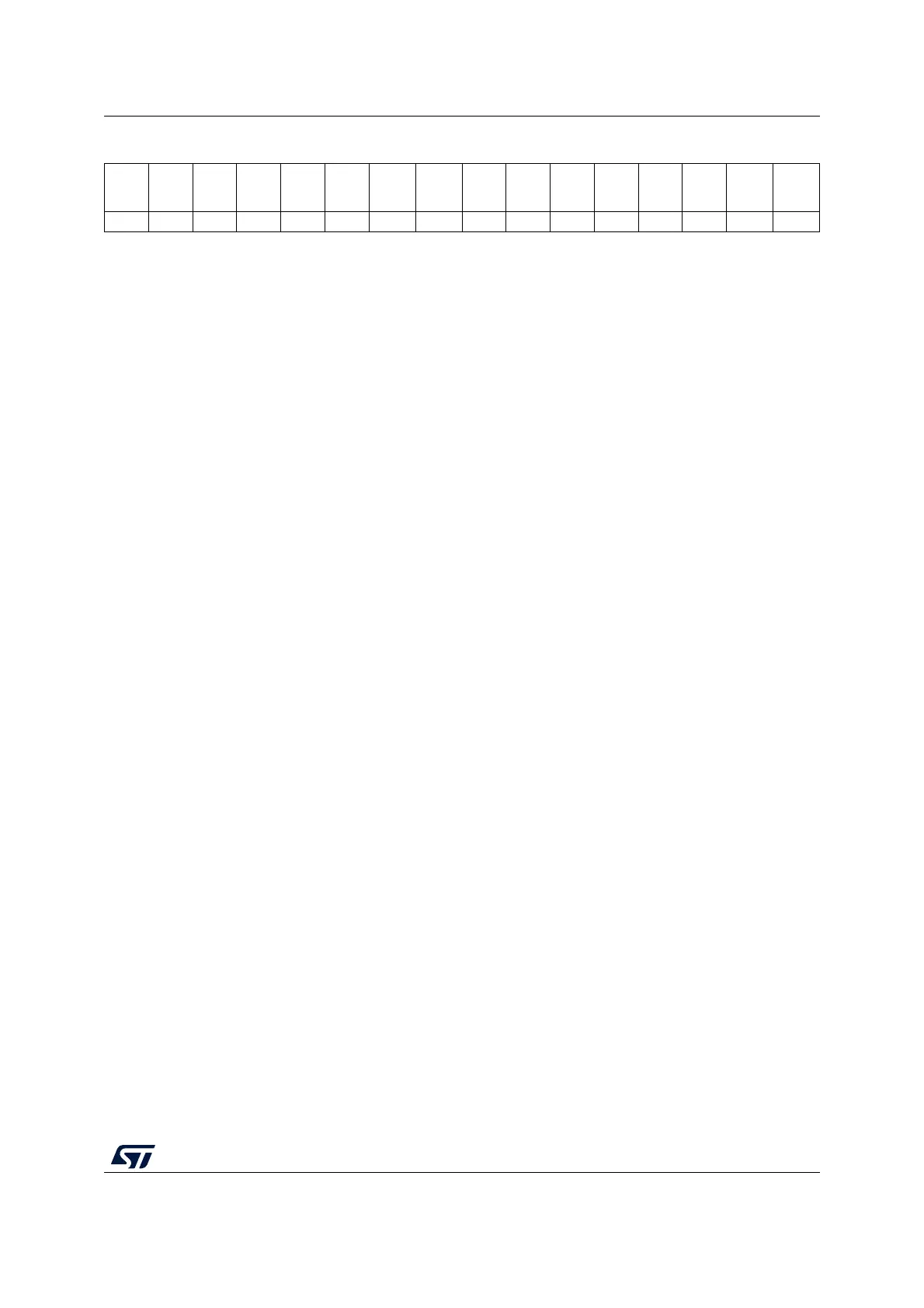

5.4.18 AHB peripheral clock enable in Sleep/Stop mode register

(RCC_AHBSMENR)

Address offset: 0x48

Reset value: 0x0005 1303

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

GPIOF

SMEN

GPIOE

SMEN

(1)

GPIOD

SMEN

GPIOC

SMEN

GPIOB

SMEN

GPIOA

SMEN

rw rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral, otherwise reserved with zero reset value. Refer to

Section 1.4: Availability of peripherals.

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 GPIOFSMEN: I/O port F clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 4 GPIOESMEN: I/O port E clock enable during Sleep mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bit 3 GPIODSMEN: I/O port D clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 2 GPIOCSMEN: I/O port C clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 1 GPIOBSMEN: I/O port B clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 0 GPIOASMEN: I/O port A clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Loading...

Loading...