RM0444 Rev 5 539/1390

RM0444 Advanced-control timer (TIM1)

624

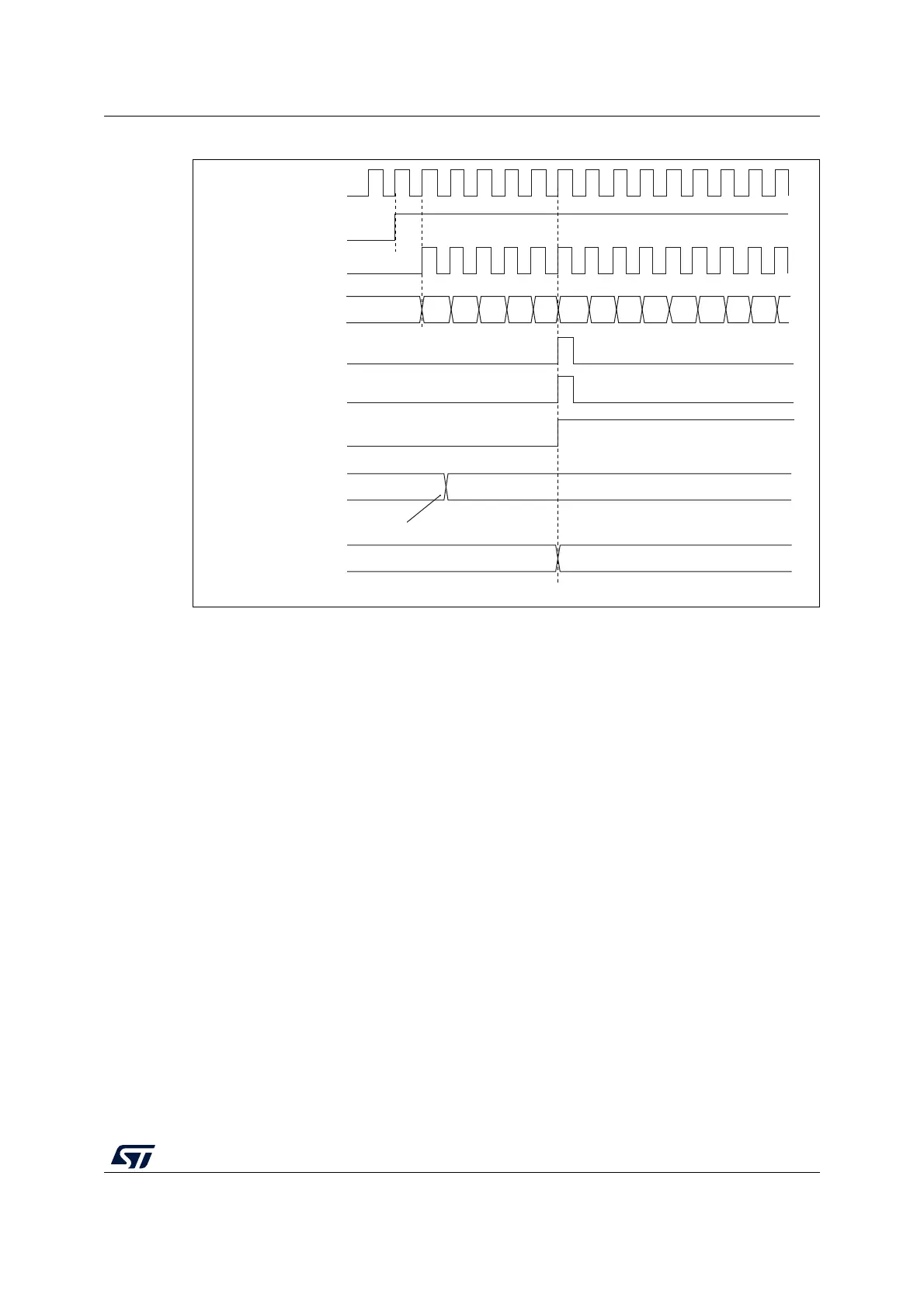

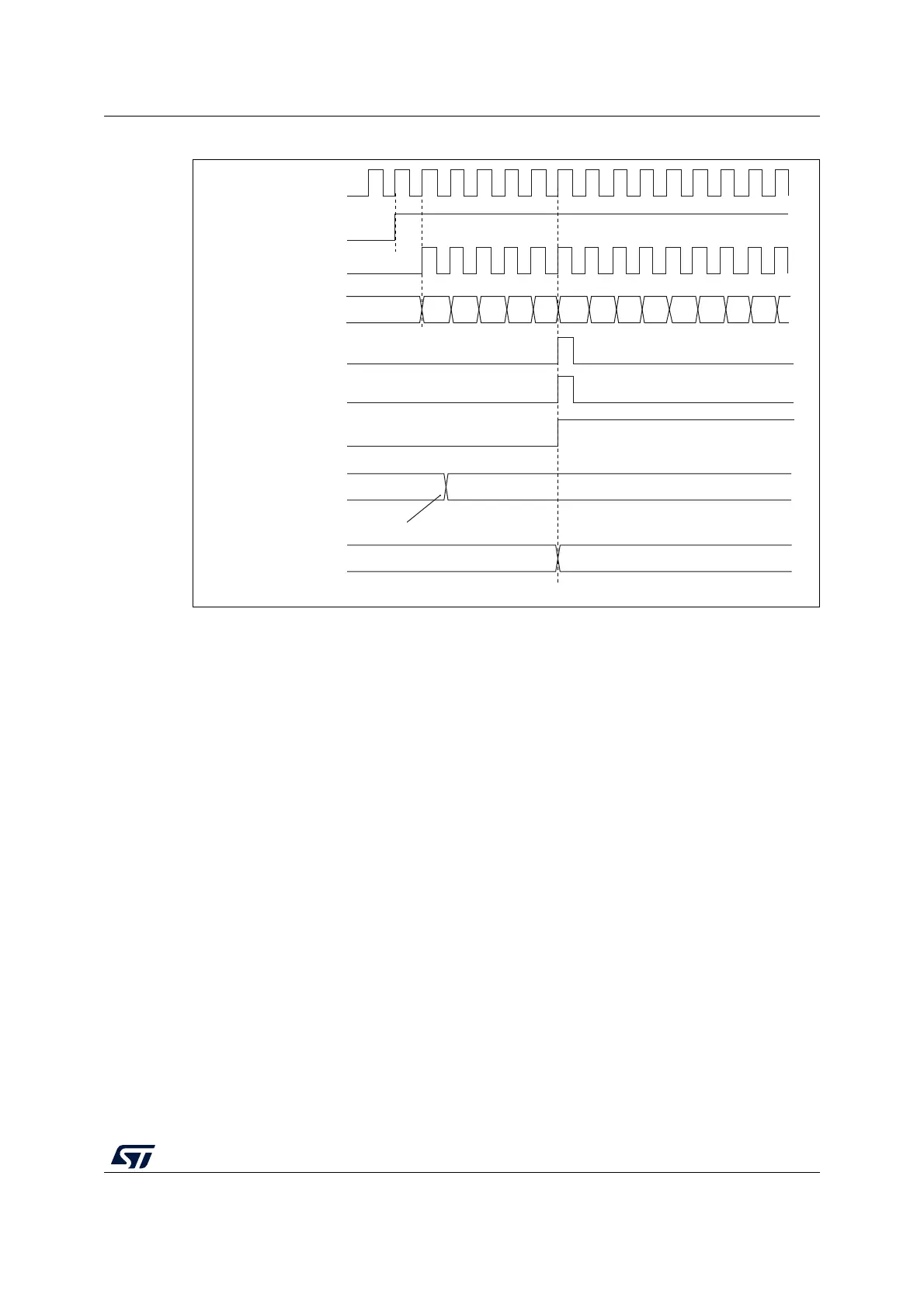

Figure 120. Counter timing diagram, Update event with ARPE=1 (counter overflow)

21.3.3 Repetition counter

Section 21.3.1: Time-base unit describes how the update event (UEV) is generated with

respect to the counter overflows/underflows. It is actually generated only when the repetition

counter has reached zero. This can be useful when generating PWM signals.

This means that data are transferred from the preload registers to the shadow registers

(TIMx_ARR auto-reload register, TIMx_PSC prescaler register, but also TIMx_CCRx

capture/compare registers in compare mode) every N+1 counter overflows or underflows,

where N is the value in the TIMx_RCR repetition counter register.

The repetition counter is decremented:

• At each counter overflow in upcounting mode,

• At each counter underflow in downcounting mode,

• At each counter overflow and at each counter underflow in center-aligned mode.

Although this limits the maximum number of repetition to 32768 PWM cycles, it makes

it possible to update the duty cycle twice per PWM period. When refreshing compare

registers only once per PWM period in center-aligned mode, maximum resolution is

2xT

ck

, due to the symmetry of the pattern.

The repetition counter is an auto-reload type; the repetition rate is maintained as defined by

the TIMx_RCR register value (refer to Figure 121). When the update event is generated by

software (by setting the UG bit in TIMx_EGR register) or by hardware through the slave

mode controller, it occurs immediately whatever the value of the repetition counter is and the

repetition counter is reloaded with the content of the TIMx_RCR register.

MS31194V1

FD

36

CK_PSC

Timer clock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag

(UIF)

36

34

33 32 31

30

2F

F8

F9

FA FB

FCF7

35

CEN

Auto-reload preload

register

Write a new value in TIMx_ARR

Auto-reload active

register

FD

36

Loading...

Loading...