AES hardware accelerator (AES) RM0444

478/1390 RM0444 Rev 5

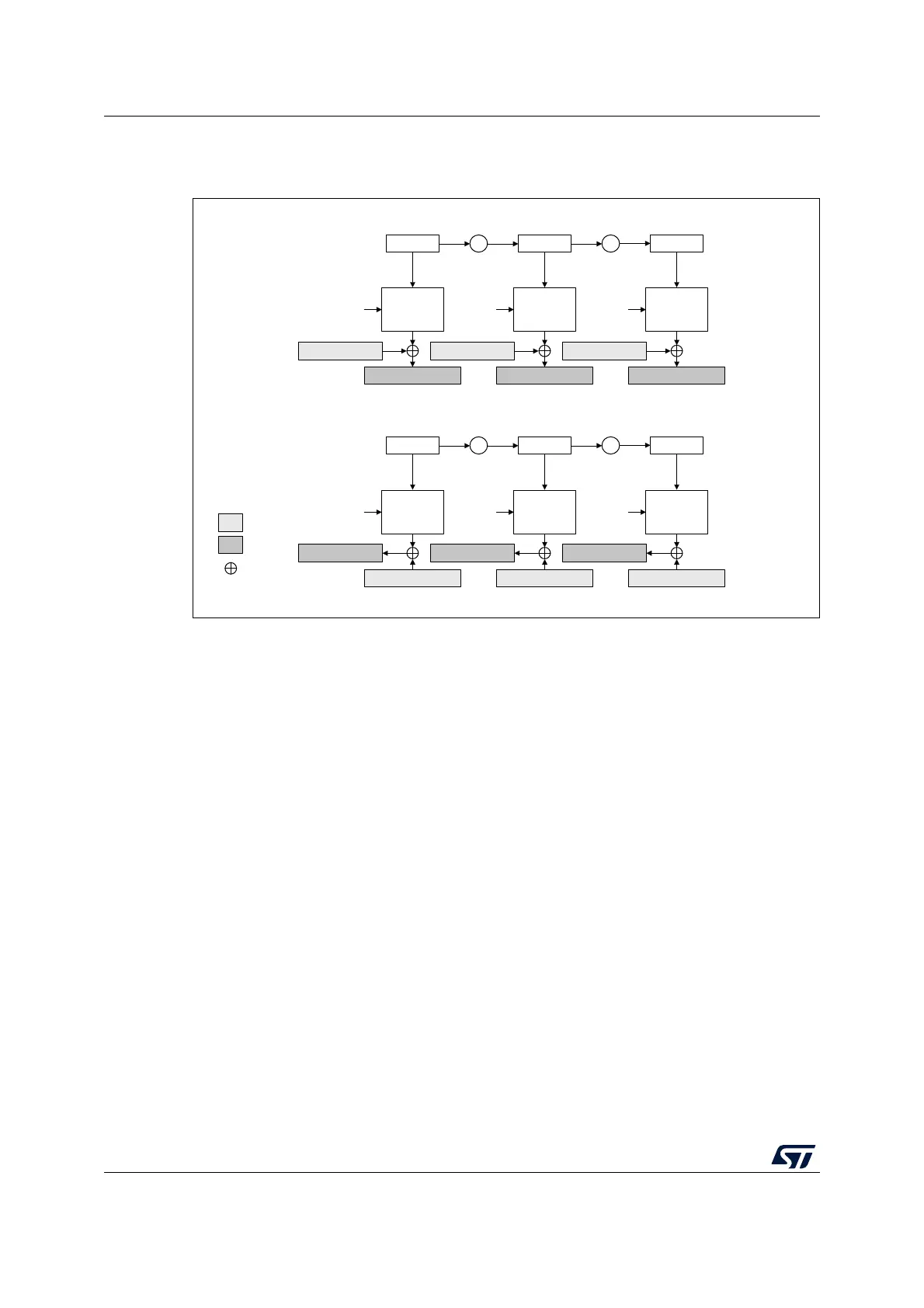

Counter (CTR) mode

Figure 78. CTR encryption and decryption principle

The CTR mode uses the AES core to generate a key stream. The keys are then XORed

with the plaintext to obtain the ciphertext as specified in NIST Special Publication 800-38A,

Recommendation for Block Cipher Modes of Operation.

Note: Unlike with ECB and CBC modes, no key scheduling is required for the CTR decryption,

since in this chaining scheme the AES core is always used in encryption mode for producing

the key stream, or counter blocks.

MSv42142V1

Encryption

Plaintext block 1

Ciphertext block 1 Ciphertext block 2 Ciphertext block 3

Encrypt Encrypt Encrypt

Decryption

Ciphertext block 1 Ciphertext block 2 Ciphertext block 3

Decrypt Decrypt Decrypt

input

output

Legend

key key key

key key key

Plaintext block 2 Plaintext block 3

Counter Counter Counter

+1 +1

Plaintext block 1 Plaintext block 2 Plaintext block 3

Counter Counter Counter

+1 +1

XOR

value value + 1 value + 2

value value + 1 value + 2

Loading...

Loading...