RM0444 Rev 5 71/1390

RM0444 Embedded Flash memory (FLASH)

118

3.3.2 FLASH empty check

During the OBL phase, after loading all options, the Flash memory interface checks whether

the first location of the Main memory is programmed. The result of this check in conjunction

with the boot0 and boot1 information is used to determine where the system has to boot

from. It prevents the system to boot from Main Flash memory area when i.e. no user code

has been programmed.

The Main Flash memory empty check status can be read from the EMPTY bit in FLASH

access control register (FLASH_ACR). Software can modify the Main Flash memory empty

status by writing an appropriate value to the EMPTY bit.

3.3.3 FLASH error code correction (ECC)

Data in Flash memory words are 72-bits wide: eight bits are added per each double word

(64 bits). The ECC mechanism supports:

• One error detection and correction

• Two errors detection

When one error is detected and corrected, the flag ECCC (ECC correction) is set in FLASH

ECC register (FLASH_ECCR). If ECCCIE is set, an interrupt is generated.

When two errors are detected, a flag ECCD (ECC detection) is set in FLASH ECC register

(FLASH_ECCR). In this case, a NMI is generated.

When an ECC error is detected, the address of the failing double word is saved in

ADDR_ECC[16:0] bitfield of the FLASH_ECCR register. ADDR_ECC[2:0] are always

cleared. The bus-ID of the CPU accessing the address is saved in CPUID[2:0].

While ECCC or ECCD is set, FLASH_ECCR is not updated if a new ECC error occurs.

FLASH_ECCR is updated only when ECC flags are cleared.

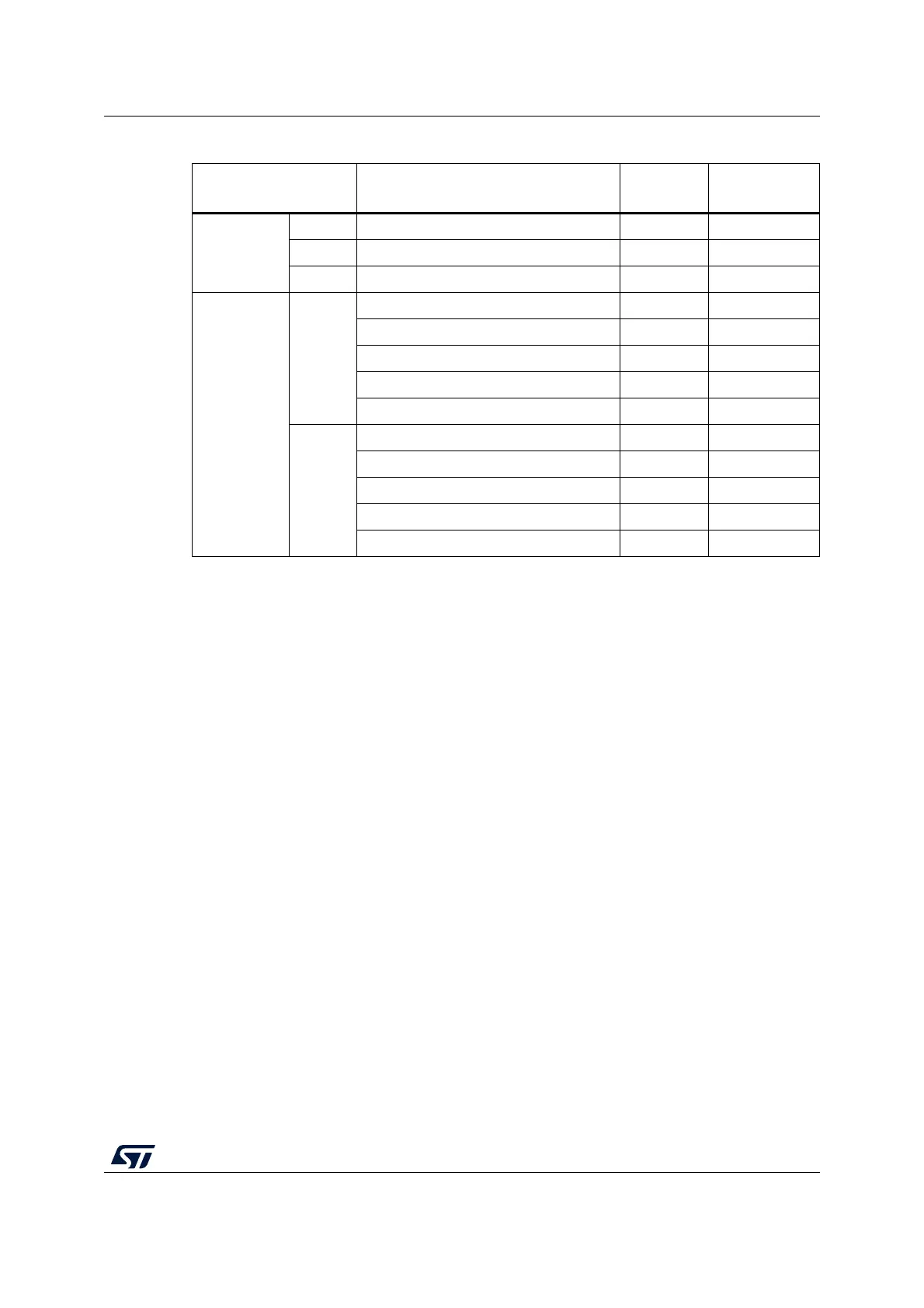

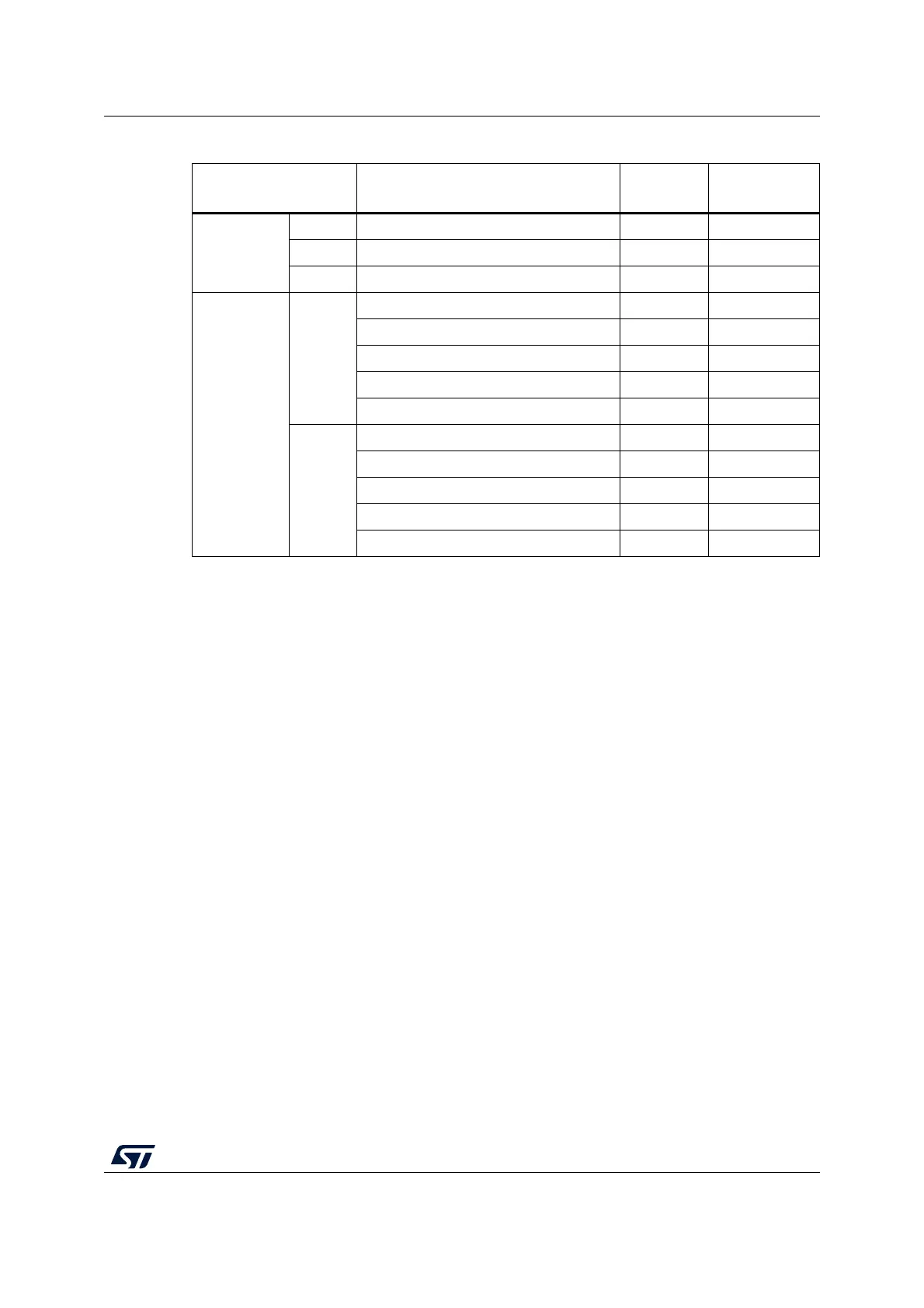

Table 11. Flash memory organization for 512 Kbytes dual-bank devices

Area Addresses Size (bytes)

Memory

type

Information

block

Bank 1 0x1FFF 7800 - 0x1FFF 787F 128 Option bytes

Bank 1 0x1FFF 7000 - 0x1FFF 73FF 1 K OTP area

Bank 1 0x1FFF 0000 - 0x1FFF 6FFF 28 K System memory

Main

memory

Bank 2

0x0807 F804 - 0x0807 FFFF 2 K Page 383

... ... ...

0x0804 1000 - 0x0804 17FF 2 K Page 258

0x0804 0800 - 0x0804 0FFF 2 K Page 257

0x0804 0000 - 0x0804 07FF 2 K Page 256

Bank 1

0x0803 F800 - 0x0803 FFFF 2 K Page 127

... ... ...

0x0800 1000 - 0x0800 17FF 2 K Page 2

0x0800 0800 - 0x0800 0FFF 2 K Page 1

0x0800 0000 - 0x0800 07FF 2 K Page 0

Loading...

Loading...