Reset and clock control (RCC) RM0444

208/1390 RM0444 Rev 5

5.4.20 APB peripheral clock enable in Sleep/Stop mode register 2

(RCC_APBSMENR2)

Address offset: 0x50

Reset value: 0x0017 D801

Bit 5 TIM7SMEN: TIM7 timer clock enable during Sleep mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bit 4 TIM6SMEN: TIM6 timer clock enable during Sleep mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bit 3 Reserved, must be kept at reset value.

Bit 2 TIM4SMEN: TIM4 timer clock enable during Sleep mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bit 1 TIM3SMEN: TIM3 timer clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 0 TIM2SMEN: TIM2 timer clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

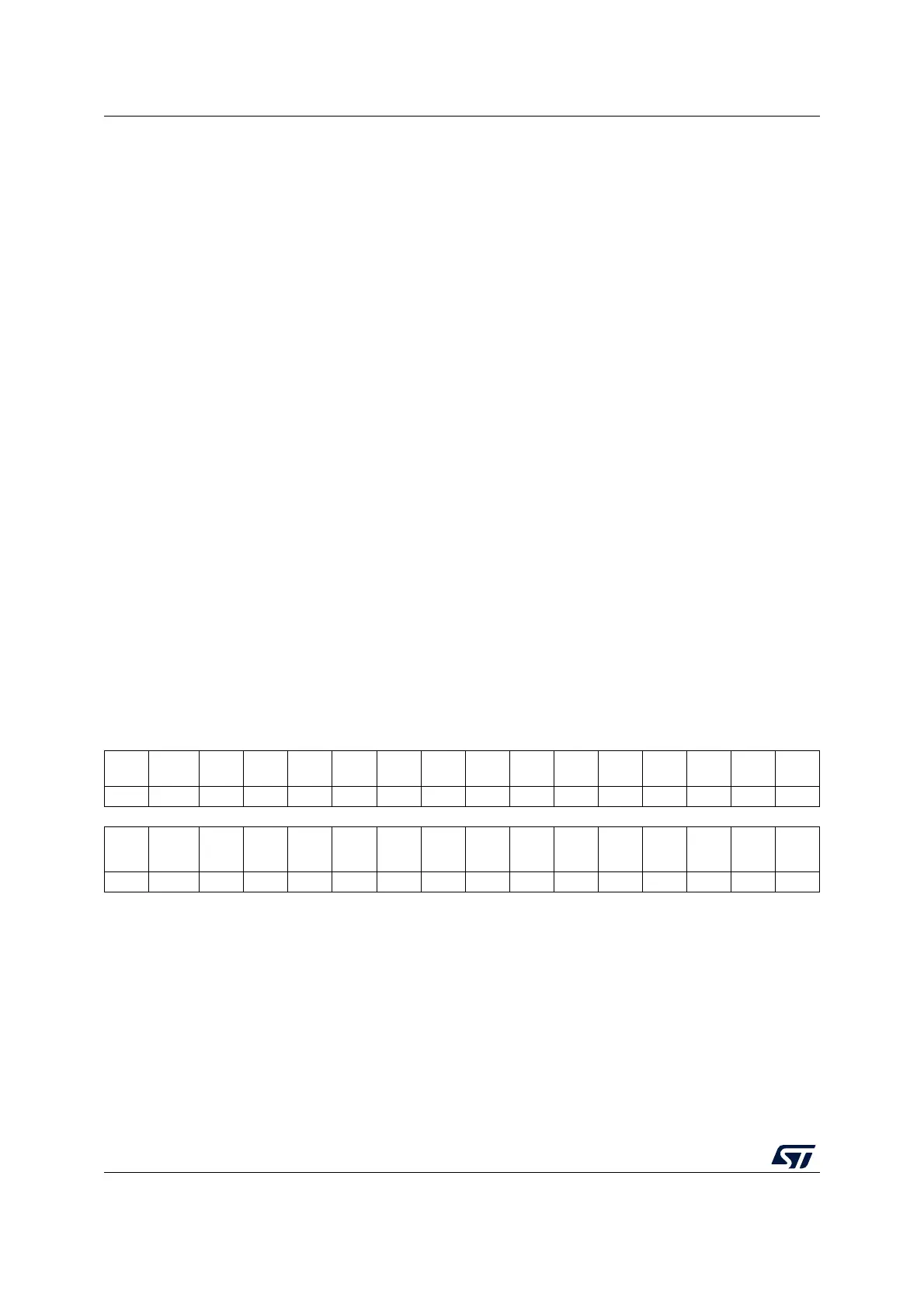

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ADC

SMEN

Res.

TIM17

SMEN

TIM16

SMEN

TIM15S

MEN

(1)

rw rw rw rw

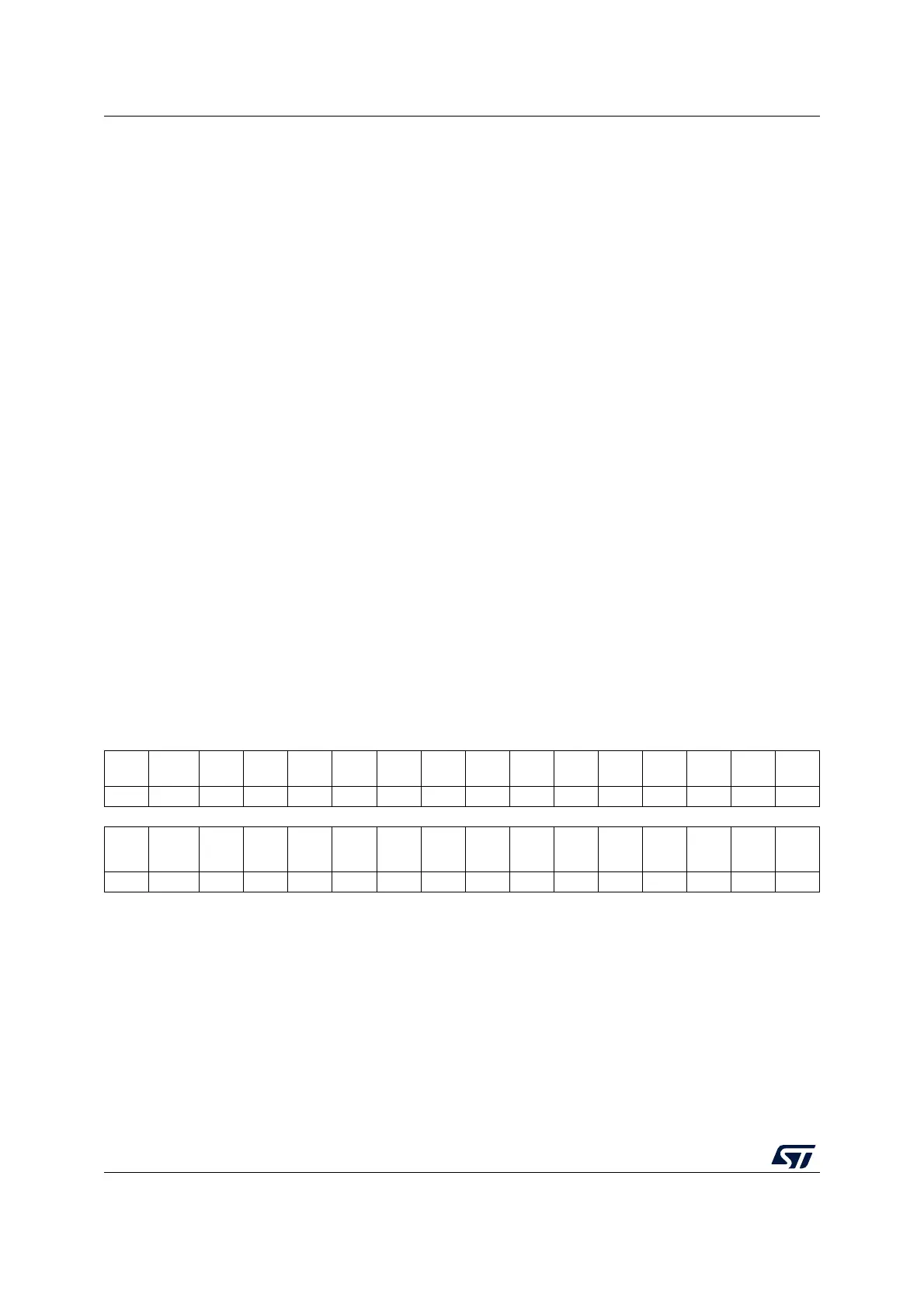

1514131211109876543210

TIM14

SMEN

USART1

SMEN

Res.

SPI1

SMEN

TIM1

SMEN

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

SYS

CFG

SMEN

rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral, otherwise reserved with zero reset value. Refer to

Section 1.4: Availability of peripherals.

Bits 31:21 Reserved, must be kept at reset value.

Bit 20 ADCSMEN: ADC clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 19 Reserved, must be kept at reset value.

Loading...

Loading...