System configuration controller (SYSCFG) RM0444

258/1390 RM0444 Rev 5

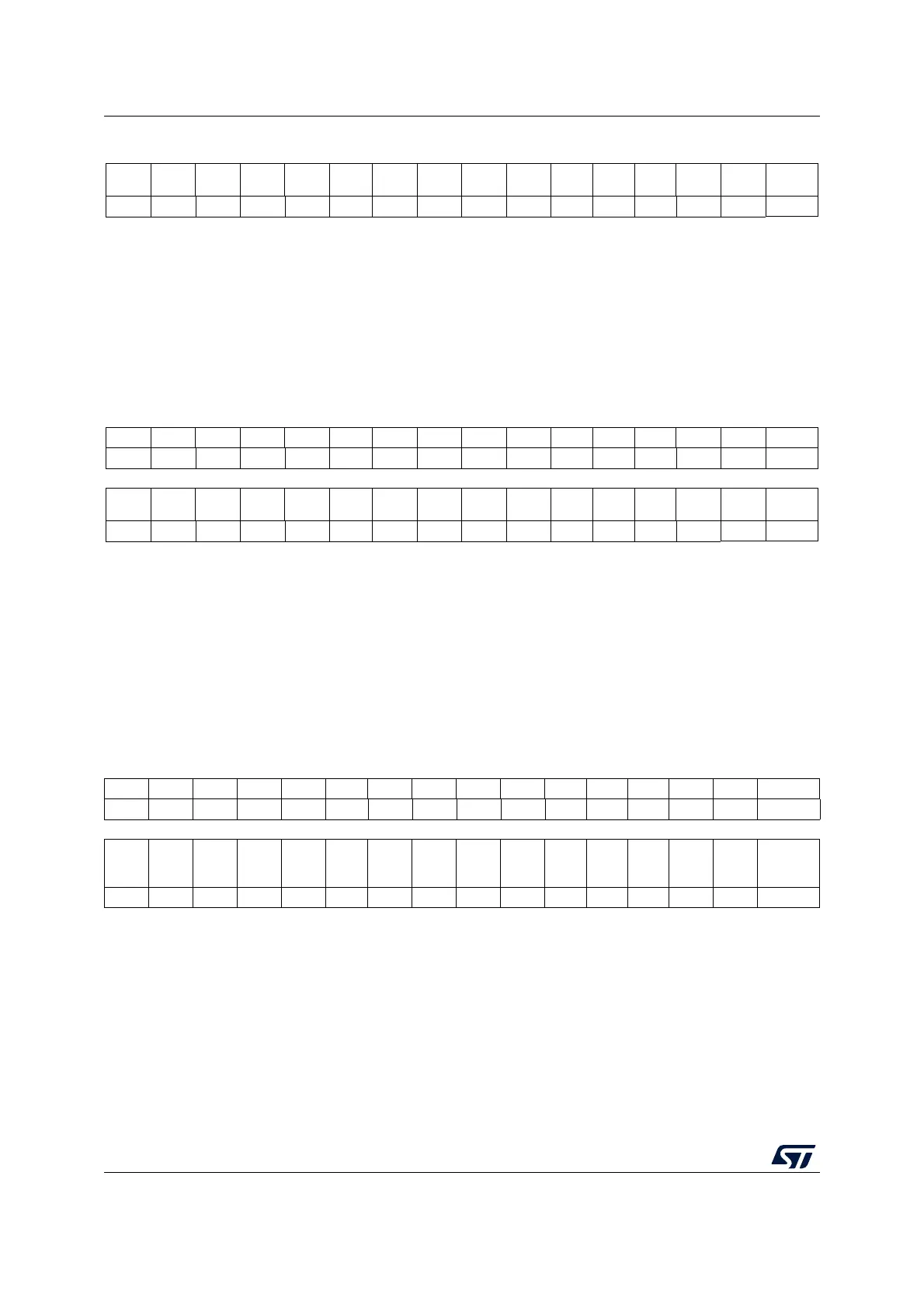

8.1.13 SYSCFG interrupt line 10 status register (SYSCFG_ITLINE10)

Address offset: 0xA8

System reset value: 0x0000 0000

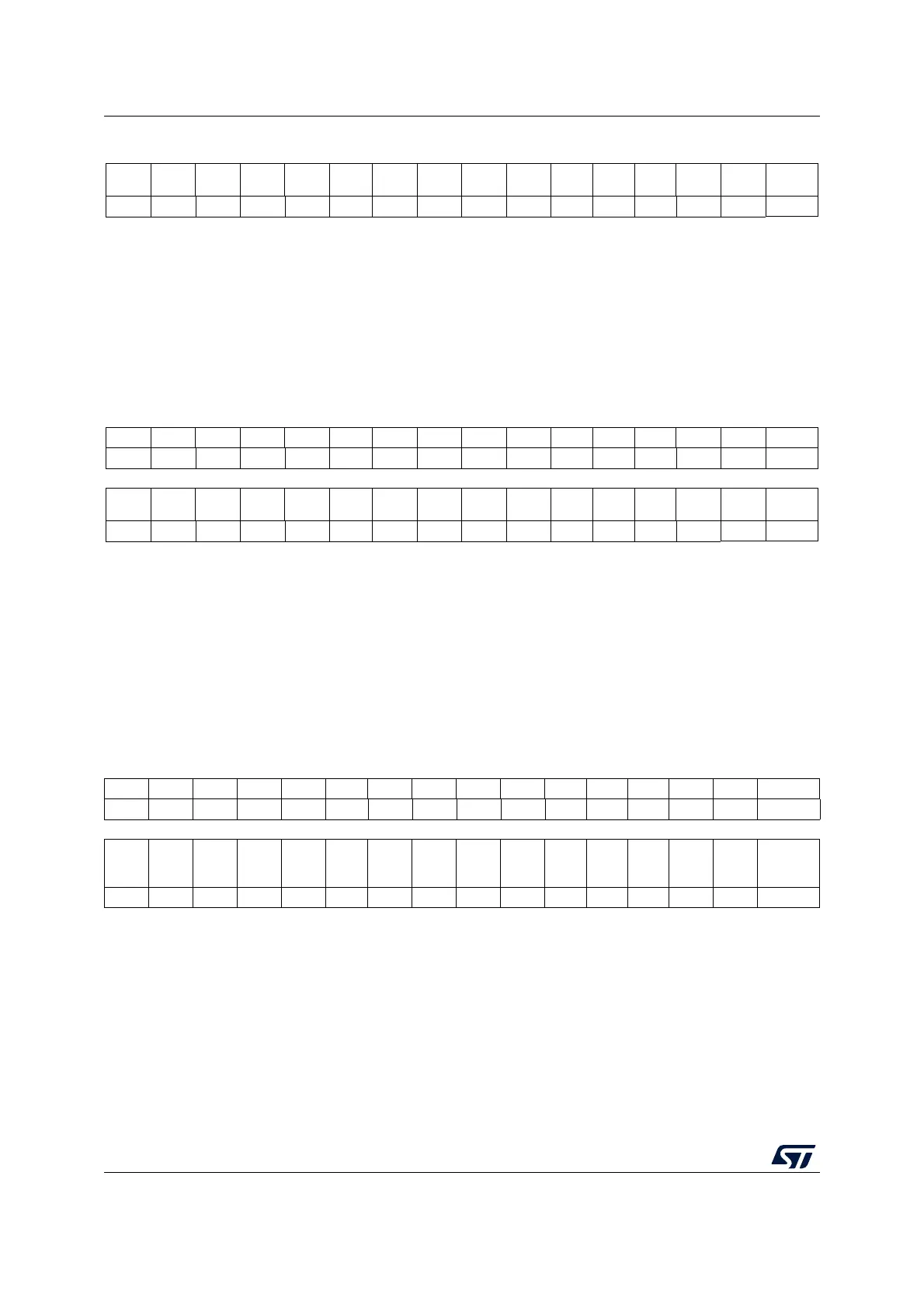

8.1.14 SYSCFG interrupt line 11 status register (SYSCFG_ITLINE11)

Address offset: 0xAC

System reset value: 0x0000 0000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DMA1_

CH1

r

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 DMA1_CH1: DMA1 channel 1 interrupt request pending

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DMA1

_CH3

DMA1

_CH2

rr

Bits 31:2 Reserved, must be kept at reset value.

Bit 1 DMA1_CH3: DMA1 channel 3 interrupt request pending

Bit 0 DMA1_CH2: DMA1 channel 2 interrupt request pending

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

151413121110987654321 0

Res. Res. Res. Res. Res. Res.

DMA2_

CH5

(1)

DMA2_

CH4

(1)

DMA2_

CH3

(1)

DMA2_

CH2

(1)

DMA2

_CH1

(1)

DMA1

_CH7

(1)

DMA1

_CH6

(1)

DMA1

_CH5

DMA1

_CH4

DMAMUX

rrrrrrrrr r

1. Only significant on devices integrating the corresponding DMA instance and channel, otherwise reserved. Refer to

Section 1.4: Availability of peripherals.

Bits 31:10 Reserved, must be kept at reset value.

Bit 9 DMA2_CH5: DMA2 channel 5 interrupt request pending

(1)

Bit 8 DMA2_CH4: DMA2 channel 4 interrupt request pending

(1)

Bit 7 DMA2_CH3: DMA2 channel 3 interrupt request pending

(1)

Bit 6 DMA2_CH2: DMA2 channel 2 interrupt request pending

(1)

Bit 5 DMA2_CH1: DMA2 channel 1 interrupt request pending

(1)

Loading...

Loading...