RM0444 Rev 5 253/1390

RM0444 System configuration controller (SYSCFG)

269

8.1.3 SYSCFG interrupt line 0 status register (SYSCFG_ITLINE0)

A dedicated set of registers is implemented on the device to collect all pending interrupt

sources associated with each interrupt line into a single register. This allows users to check

by single read which peripheral requires service in case more than one source is associated

to the interrupt line.

All bits in those registers are read only, set by hardware when there is corresponding

interrupt request pending and cleared by resetting the interrupt source flags in the

peripheral registers.

Address offset: 0x80

System reset value: 0x0000 0000

Bits 7:4 Reserved, must be kept at reset value.

Bit 3 ECC_LOCK: ECC error lock bit

This bit is set by software and cleared by a system reset. It can be used to enable and lock

the Flash ECC 2-bit error detection signal connection to TIM1/15/16/17 Break input.

0: ECC error disconnected from TIM1/15/16/17 Break input

1: ECC error connected to TIM1/15/16/17 Break input

Bit 2 PVD_LOCK: PVD lock enable bit

This bit is set by software and cleared by a system reset. It can be used to enable and lock

the PVD connection to TIM1/15/16/17 Break input, as well as the PVDE and PLS[2:0] in the

PWR_CR register.

0: PVD interrupt disconnected from TIM1/15/16/17 Break input. PVDE and PLS[2:0] bits can

be programmed by the application.

1: PVD interrupt connected to TIM1/15/16/17 Break input, PVDE and PLS[2:0] bits are read

only.

Bit 1 SRAM_PARITY_LOCK: SRAM parity lock bit

This bit is set by software and cleared by a system reset. It can be used to enable and lock

the SRAM parity error signal connection to TIM1/15/16/17 Break input.

0: SRAM parity error disconnected from TIM1/15/16/17 Break input

1: SRAM parity error connected to TIM1/15/16/17 Break input

Bit 0 LOCKUP_LOCK: Cortex

®

-M0+ LOCKUP bit enable bit

This bit is set by software and cleared by a system reset. It can be use to enable and lock the

connection of Cortex

®

-M0+ LOCKUP (Hardfault) output to TIM1/15/16/17 Break input.

0: Cortex

®

-M0+ LOCKUP output disconnected from TIM1/15/16/17 Break input

1: Cortex

®

-M0+ LOCKUP output connected to TIM1/15/16/17 Break input

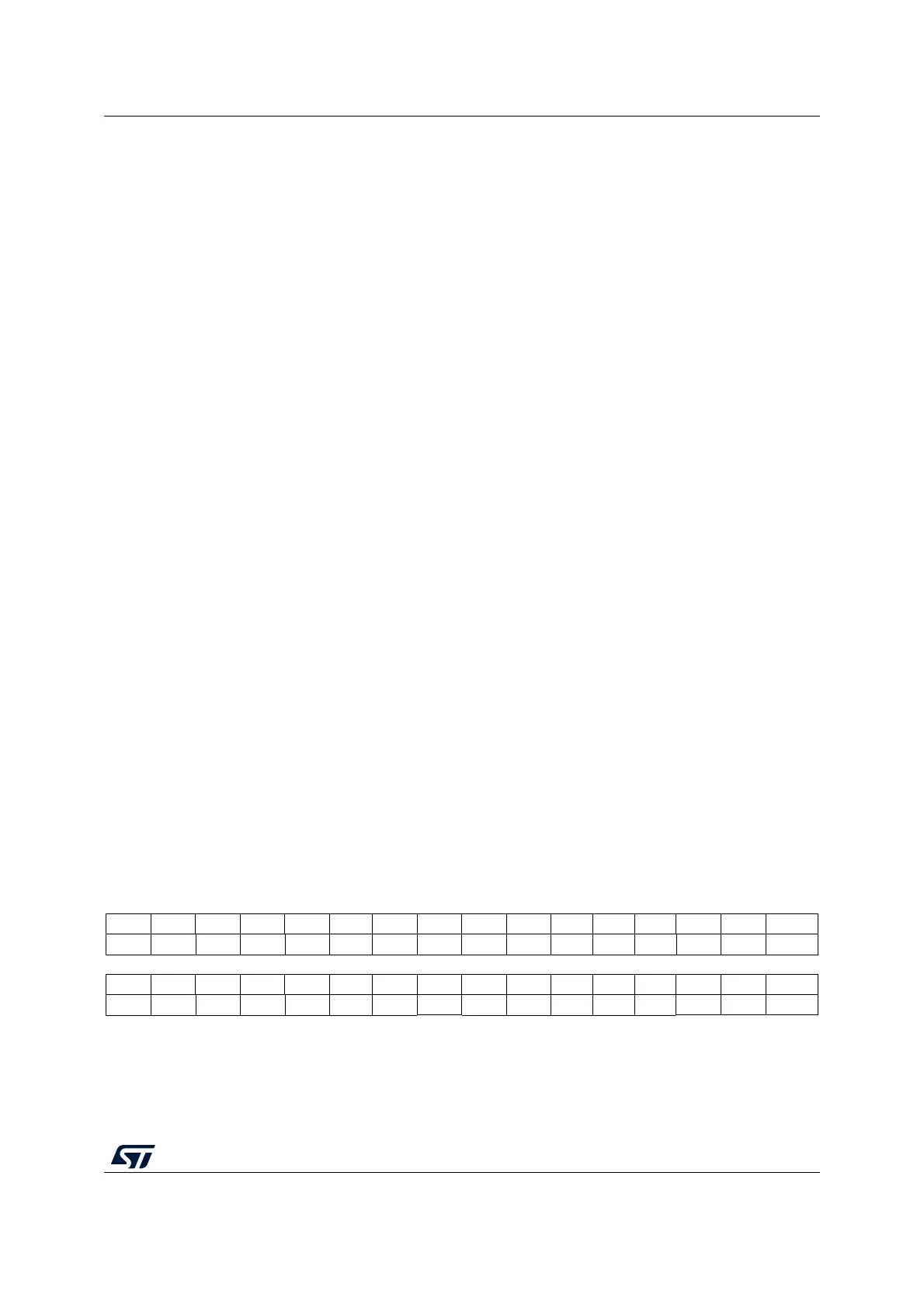

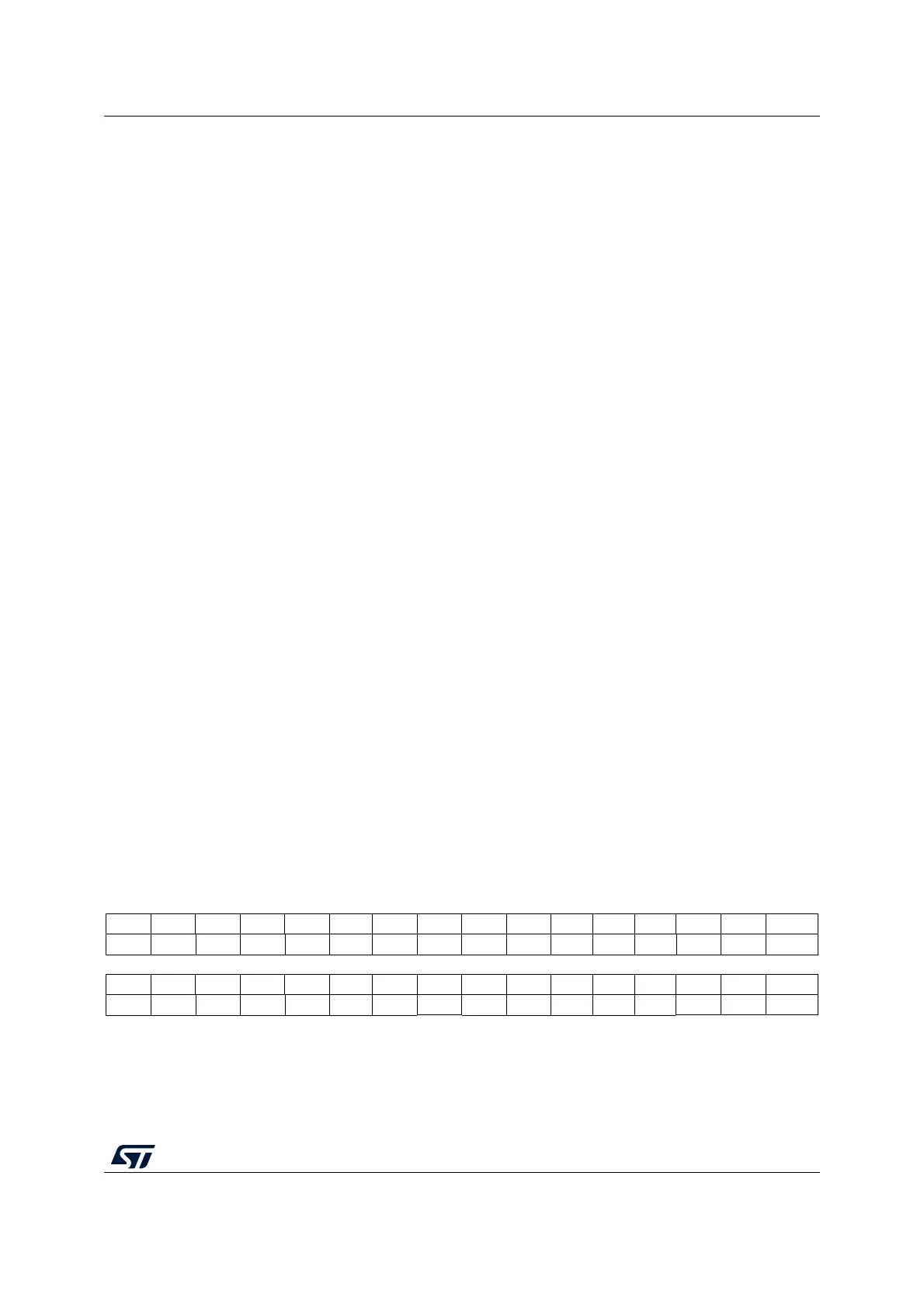

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. WWDG

r

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 WWDG: Window watchdog interrupt pending flag

Loading...

Loading...