Universal serial bus full-speed host/device interface (USB) RM0444

1278/1390 RM0444 Rev 5

The isochronous behavior for an endpoint is selected by setting the UTYPE bits at 10 in its

USB_CHEPnR register; since there is no handshake phase the only legal values for the

STATRX/STATTX bit pairs are 00 (DISABLED) and 11 (VALID), any other value produces

results not compliant to USB standard. Isochronous endpoints implement double-buffering

to ease application software development, using both ‘transmission’ and ‘reception’ packet

memory areas to manage buffer swapping on each successful transaction in order to have

always a complete buffer to be used by the application, while the USB peripheral fills the

other.

The memory buffer which is currently used by the USB peripheral is defined by the DTOG

bit related to the endpoint direction (DTOGRX for ‘reception’ isochronous endpoints,

DTOGTX for ‘transmission’ isochronous endpoints, both in the related USB_CHEPnR

register) according to Table 220.

As it happens with double-buffered bulk endpoints, the USB_CHEPnR registers used to

implement isochronous endpoints are forced to be used as unidirectional ones. In case it is

required to have isochronous endpoints enabled both for reception and transmission, two

USB_CHEPnR registers must be used.

The application software is responsible for the DTOG bit initialization according to the first

buffer to be used; this has to be done considering the special toggle-only property that these

two bits have. At the end of each transaction, the VTRX or VTTX bit of the addressed

endpoint USB_CHEPnR register is set, depending on the enabled direction. At the same

time, the affected DTOG bit in the USB_CHEPnR register is hardware toggled making buffer

swapping completely software independent. STAT bit pair is not affected by transaction

completion; since no flow control is possible for isochronous transfers due to the lack of

handshake phase, the endpoint remains always 11 (VALID). CRC errors or buffer-overrun

conditions occurring during isochronous OUT transfers are anyway considered as correct

transactions and they always trigger a VTRX event. However, CRC errors set the ERR bit in

the USB_ISTR register anyway, in order to notify the software of the possible data

corruption.

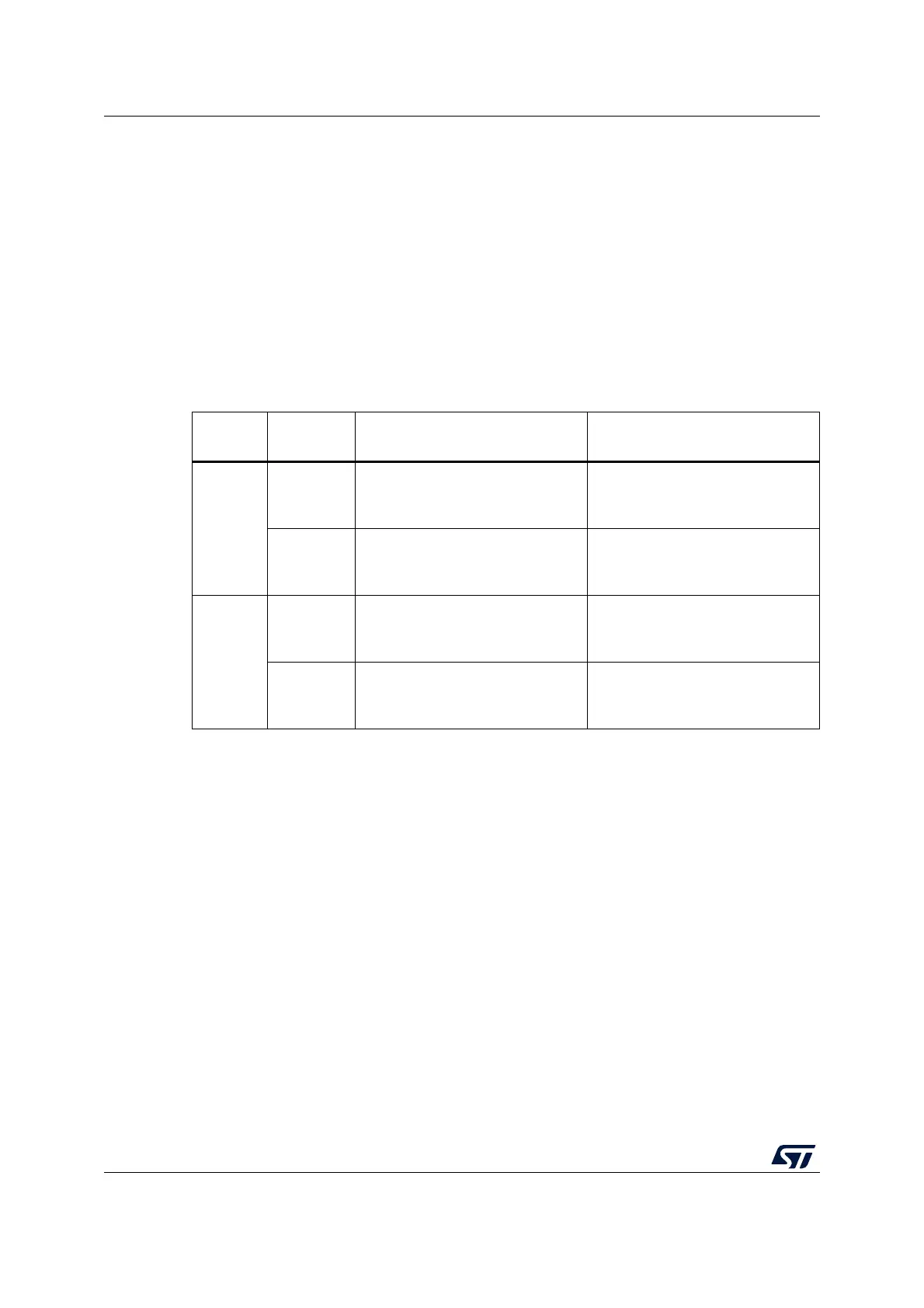

Table 220. Isochronous memory buffers usage

Endpoint

Type

DTOG bit

value

Packet buffer used by the

USB peripheral

Packet buffer used by the

application software

Transmit

(IN)

0

USB_CHEP_TXRXBD_0

(ADDRn_TX_0 / COUNTn_TX_0)

Buffer description table locations.

USB_CHEP_RXTXBD_0

(ADDRn_TX_1 / COUNTn_TX_1)

Buffer description table locations

1

USB_CHEP_RXTXBD_0

(ADDRn_TX_0 / COUNTn_TX_0)

Buffer description table locations

USB_CHEP_TXRXBD_0

(ADDRn_TX_0 / COUNTn_TX_0)

Buffer description table locations.

Receive

(OUT)

0

USB_CHEP_RXTXBD_0

(ADDRn_RX_0 / COUNTn_RX_0)

Buffer description table locations.

USB_CHEP_TXRXBD_0

(ADDRn_RX_0 / COUNTn_RX_0)

Buffer description table locations.

1

USB_CHEP_TXRXBD_0

(ADDRn_RX_0 / COUNTn_RX_0)

Buffer description table locations

USB_CHEP_RXTXBD_0

(ADDRn_RX_0 / COUNTn_RX_0)

Buffer description table locations.

Loading...

Loading...