HDMI-CEC controller (CEC) RM0444

1350/1390 RM0444 Rev 5

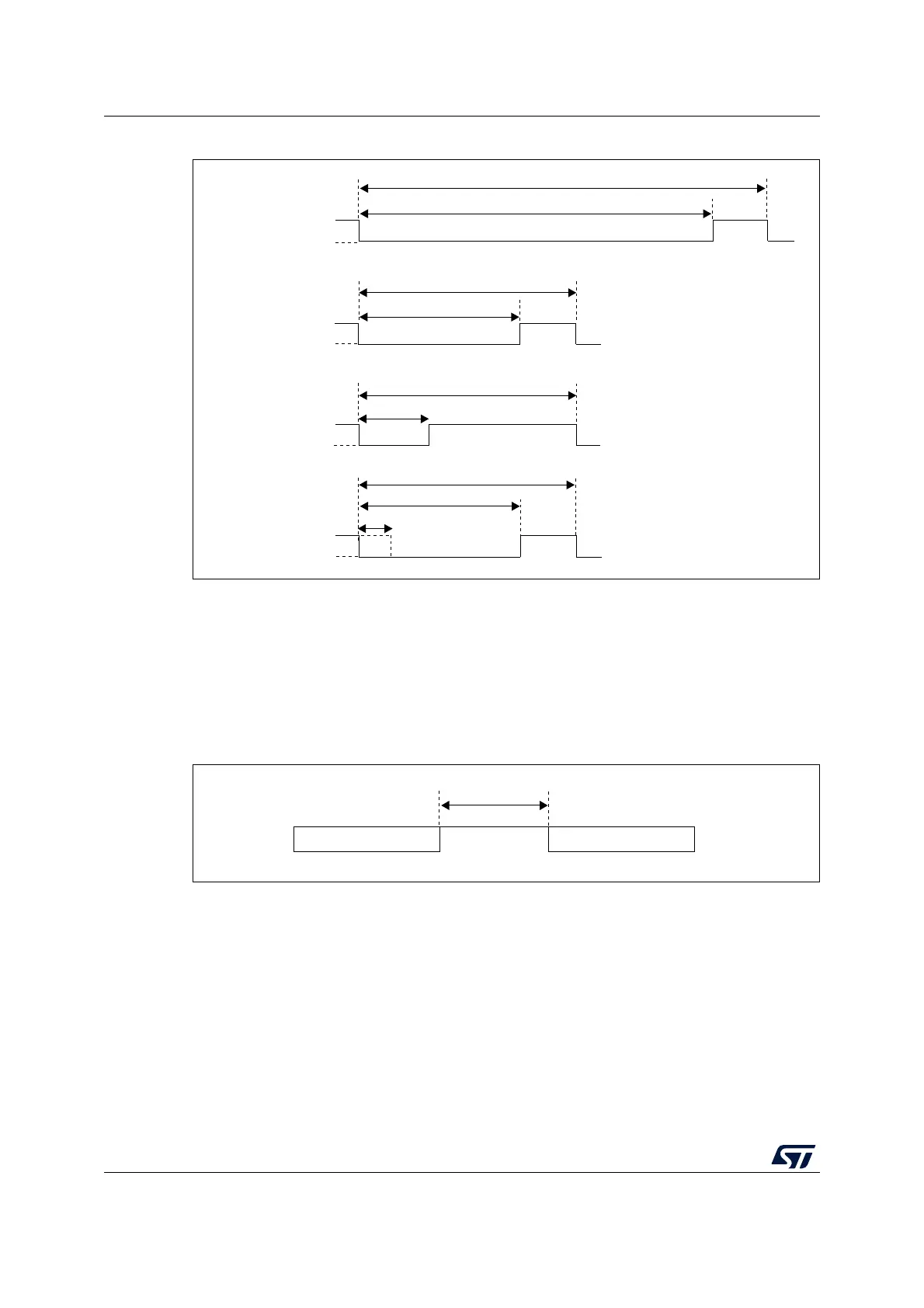

Figure 417. Bit timings

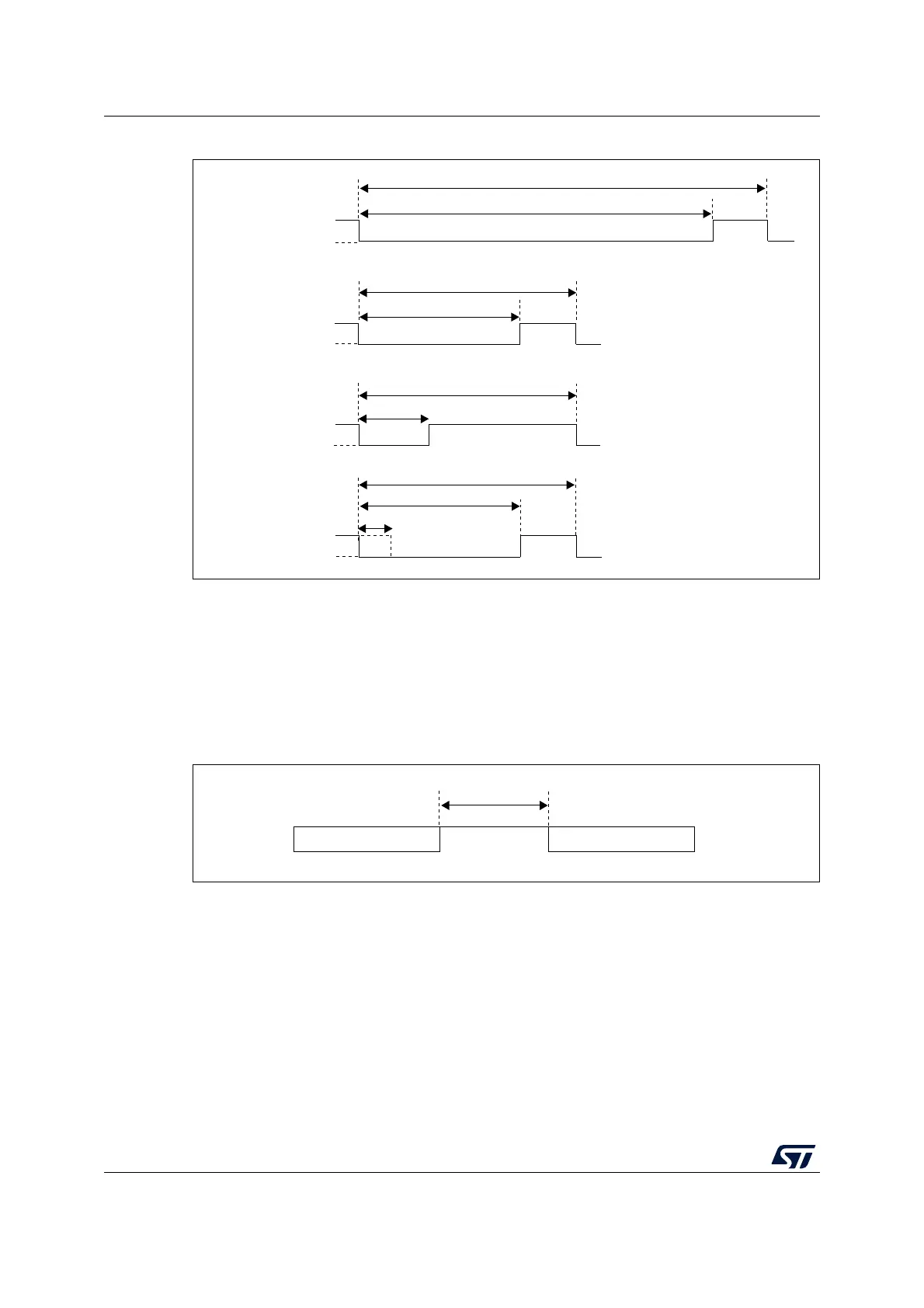

39.4 Arbitration

All devices transmitting - or retransmitting - a message onto the CEC line must ensure that it

has been inactive for a number of bit periods. This signal-free time is defined as the time

starting from the final bit of the previous frame and depends on the initiating device and the

current status as shown in the figure below.

Figure 418. Signal free time

Since only one initiator is allowed at any one time, an arbitration mechanism is provided to

avoid conflict when more than one initiator begins transmitting at the same time.

CEC line arbitration starts with the leading edge of the start bit and continues until the end of

the initiator address bits within the header block. During this period, the initiator must

monitor the CEC line, if whilst driving the line to high impedance it reads it back to 0.

Assuming then it has lost arbitration, it stops transmitting and becomes a follower.

START BIT

high impedance

low impedance

3.7 ms +/-0.2 ms

4.5 ms +/-0.2 ms

DATA BIT

high impedance

low impedance

1.5 ms +/-0.2 ms

2.4 ms +/-0.35 ms

INITIATOR LOGICAL 0

DATA BIT

high impedance

low impedance

0.6 ms +/-0.2 ms

2.4 ms +/-0.35 ms

INITIATOR LOGICAL 1

DATA BIT

high impedance

low impedance

0.35 ms max

2.4 ms +/-0.35 ms

FOLLOWER LOGICAL 0

MS31006V1

1.5 ms +/-0.2 ms

MS31007V1

PREVIOUS MESSAGE

NEW MESSAGE

Signal free time

Loading...

Loading...