System window watchdog (WWDG) RM0444

870/1390 RM0444 Rev 5

As an example, lets assume APB frequency is equal to 48 MHz, WDGTB[1:0] is set to 3 and

T[5:0] is set to 63:

Refer to the datasheet for the minimum and maximum values of the t

WWDG

.

29.3.5 Debug mode

When the device enters debug mode (processor halted), the WWDG counter either

continues to work normally or stops, depending on the configuration bit in DBG module. For

more details refer to Section 40: Debug support (DBG).

29.4 WWDG interrupts

The early wakeup interrupt (EWI) can be used if specific safety operations or data logging

must be performed before the actual reset is generated. The EWI interrupt is enabled by

setting the EWI bit in the WWDG_CFR register. When the down-counter reaches the value

0x40, an EWI interrupt is generated and the corresponding interrupt service routine (ISR)

can be used to trigger specific actions (such as communications or data logging), before

resetting the device.

In some applications, the EWI interrupt can be used to manage a software system check

and/or system recovery/graceful degradation, without generating a WWDG reset. In this

case, the corresponding interrupt service routine (ISR) has to reload the WWDG counter to

avoid the WWDG reset, then trigger the required actions.

The EWI interrupt is cleared by writing '0' to the EWIF bit in the WWDG_SR register.

Note: When the EWI interrupt cannot be served, e.g. due to a system lock in a higher priority task,

the WWDG reset is eventually generated.

29.5 WWDG registers

Refer to Section 1.2 on page 53 for a list of abbreviations used in register descriptions.

The peripheral registers can be accessed by halfwords (16-bit) or words (32-bit).

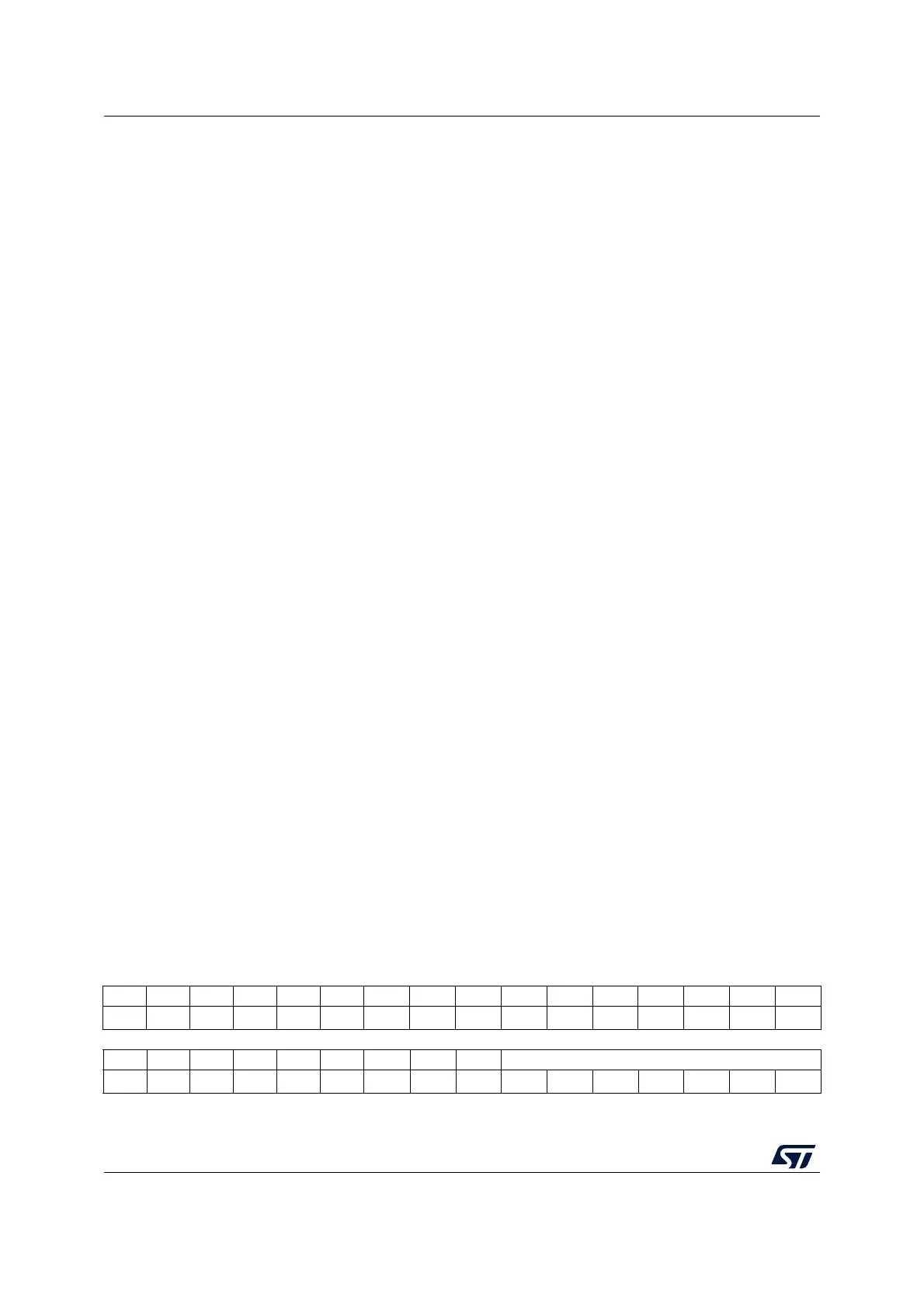

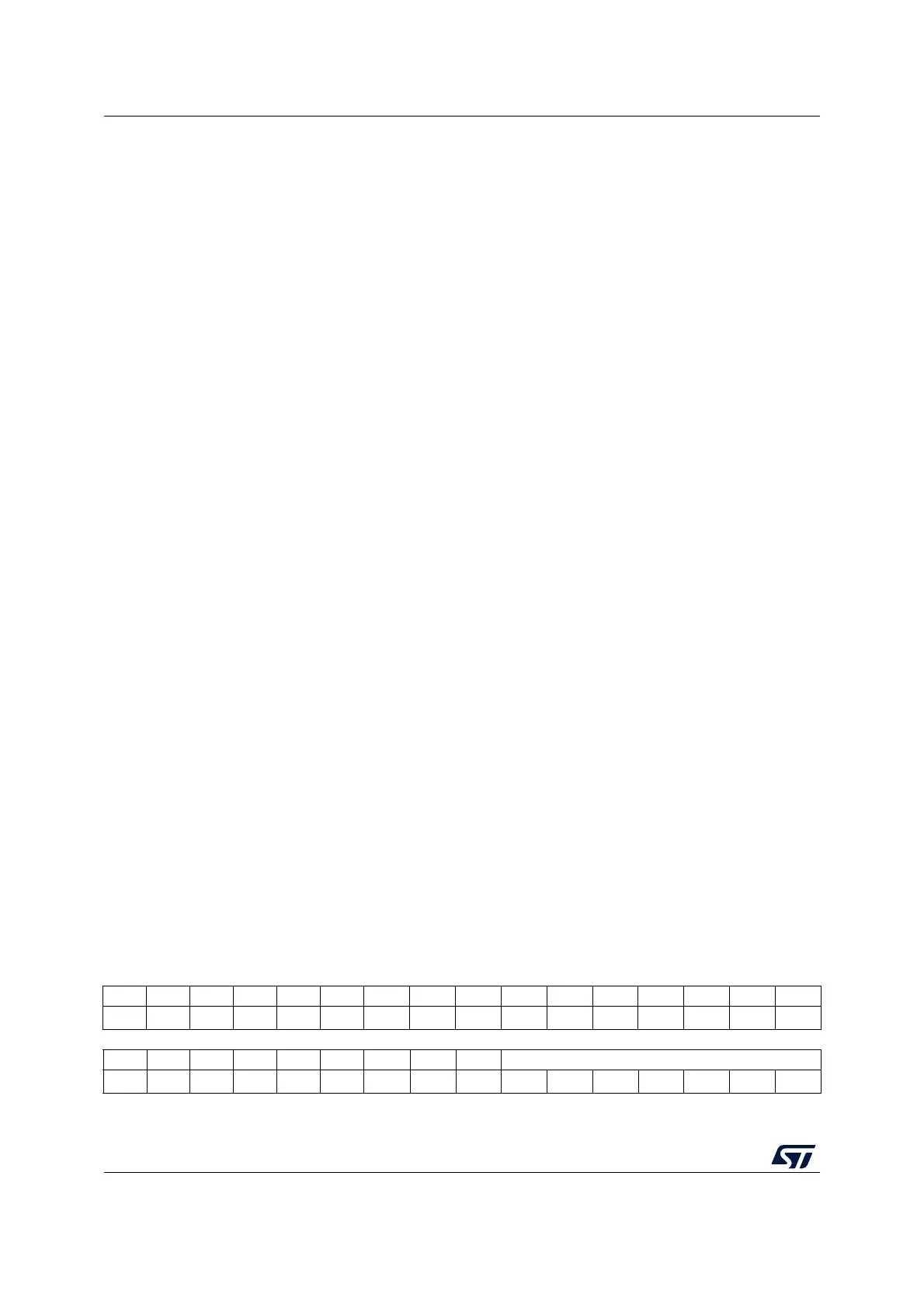

29.5.1 WWDG control register (WWDG_CR)

Address offset: 0x000

Reset value: 0x0000 007F

t

WWDG

1 48000⁄()4096 2

3

×× 63 1+()× 43.69ms==

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. WDGA T[6:0]

rs rw rw rw rw rw rw rw

Loading...

Loading...