RM0444 Rev 5 541/1390

RM0444 Advanced-control timer (TIM1)

624

21.3.4 External trigger input

The timer features an external trigger input ETR. It can be used as:

• external clock (external clock mode 2, see Section 21.3.5)

• trigger for the slave mode (see Section 21.3.26)

• PWM reset input for cycle-by-cycle current regulation (see Section 21.3.7)

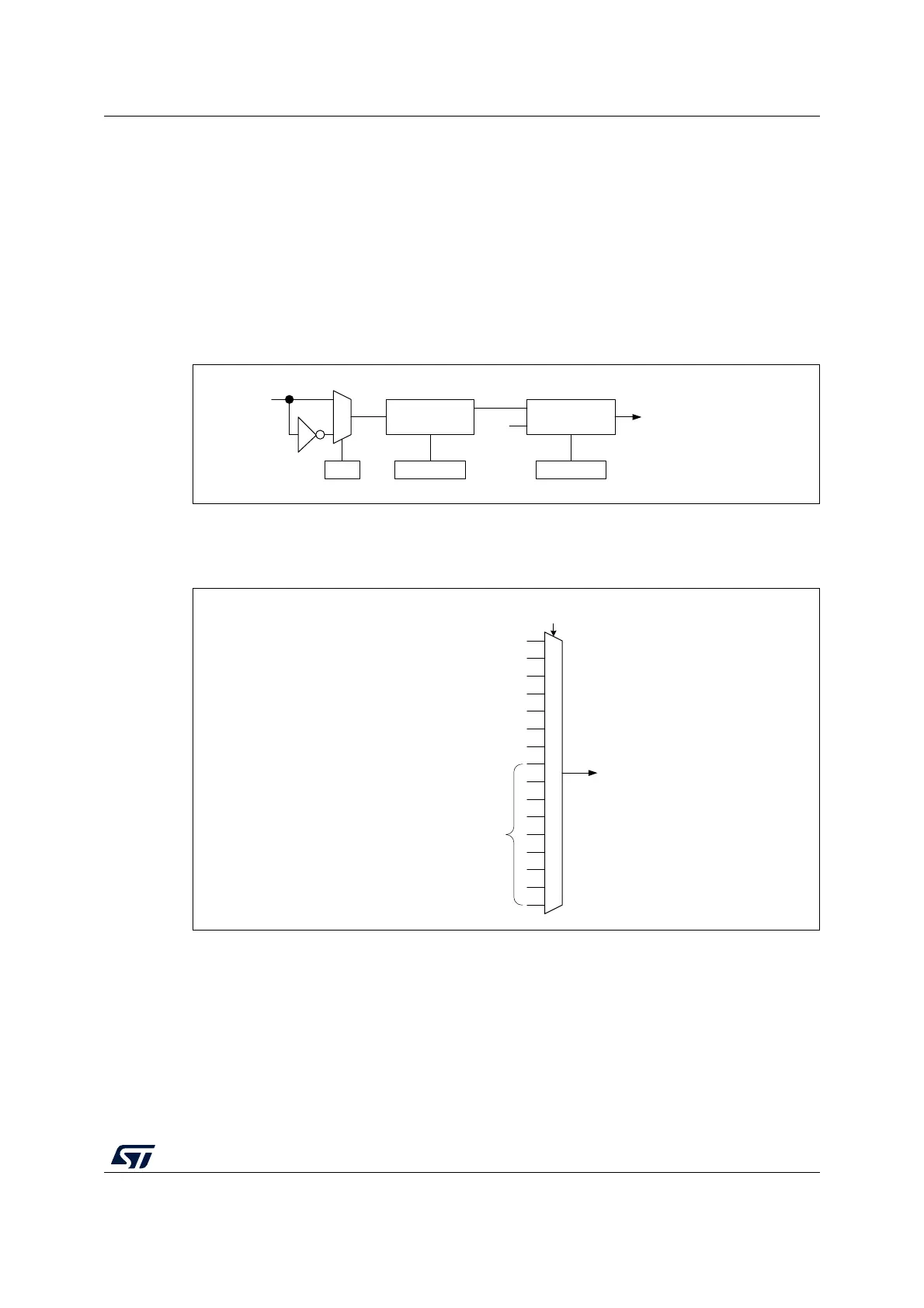

Figure 122 below describes the ETR input conditioning. The input polarity is defined with the

ETP bit in TIMxSMCR register. The trigger can be prescaled with the divider programmed

by the ETPS[1:0] bitfield and digitally filtered with the ETF[3:0] bitfield.

Figure 122. External trigger input block

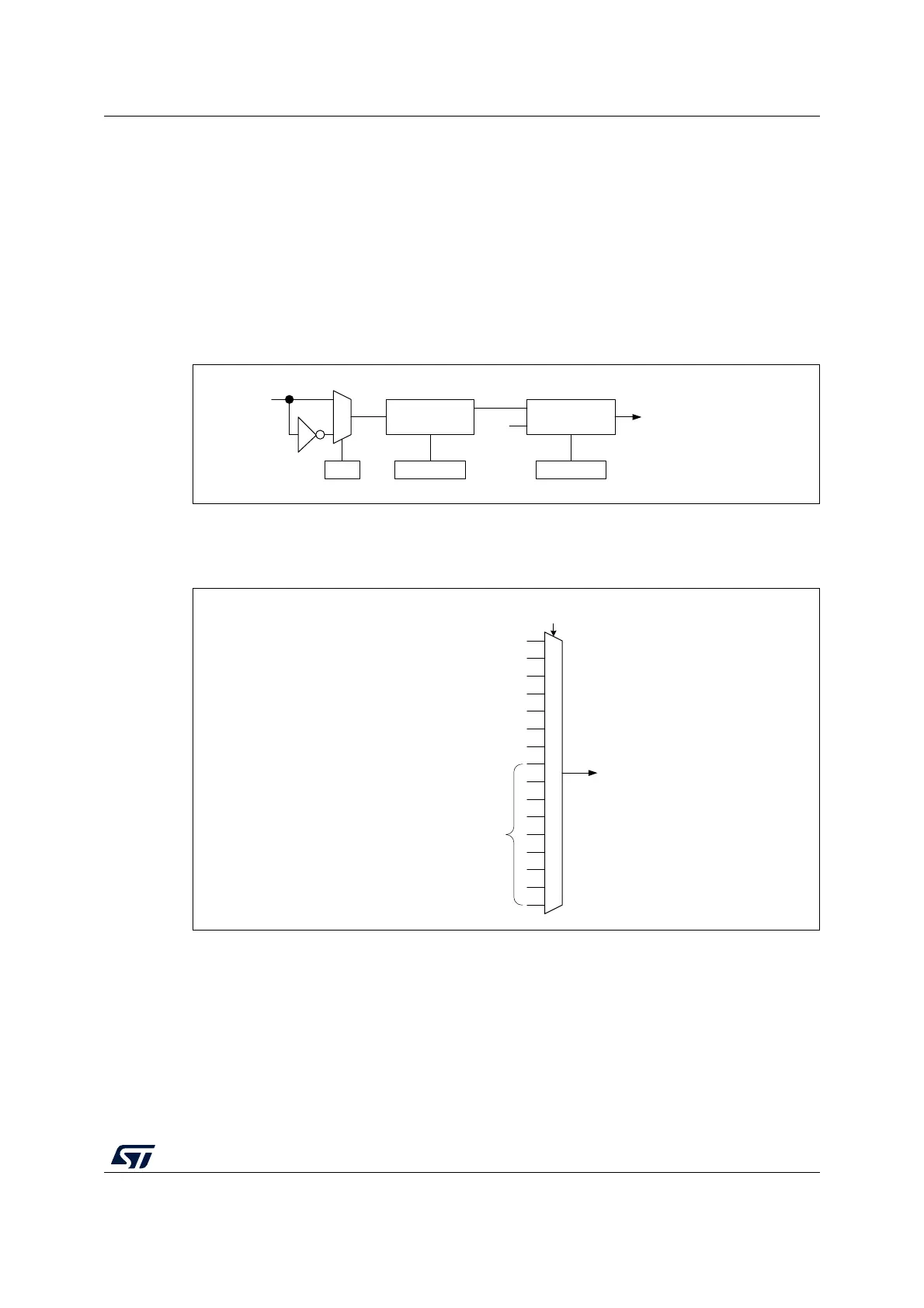

The ETR input comes from multiple sources: input pins (default configuration), comparator

outputs and analog watchdogs. The selection is done with the ETRSEL[3:0] bitfield.

Figure 123. TIM1 ETR input circuitry

1. Available on STM32G0B1xx and STM32G0C1xx salestypes only.

MS34403V2

To the Output mode controller

To the CK_PSC circuitry

To the Slave mode controller

0

1

ETR input

ETR

ETP

TIMx_SMCR

Divider

/1, /2, /4, /8

ETPS[1:0]

TIMx_SMCR

Filter

downcounter

ETF[3:0]

TIMx_SMCR

ETRP

f

DTS

MSv45739V2

TIM1_AF1[17:14]

ETR input

ETR inputs from AF controller

COMP1 output

COMP2 output

NC

ADC1 AWD1

ADC1 AWD2

ADC1 AWD3

COMP3

(1)

Loading...

Loading...