RM0444 Rev 5 1159/1390

RM0444 Serial peripheral interface / integrated interchip sound (SPI/I2S)

1195

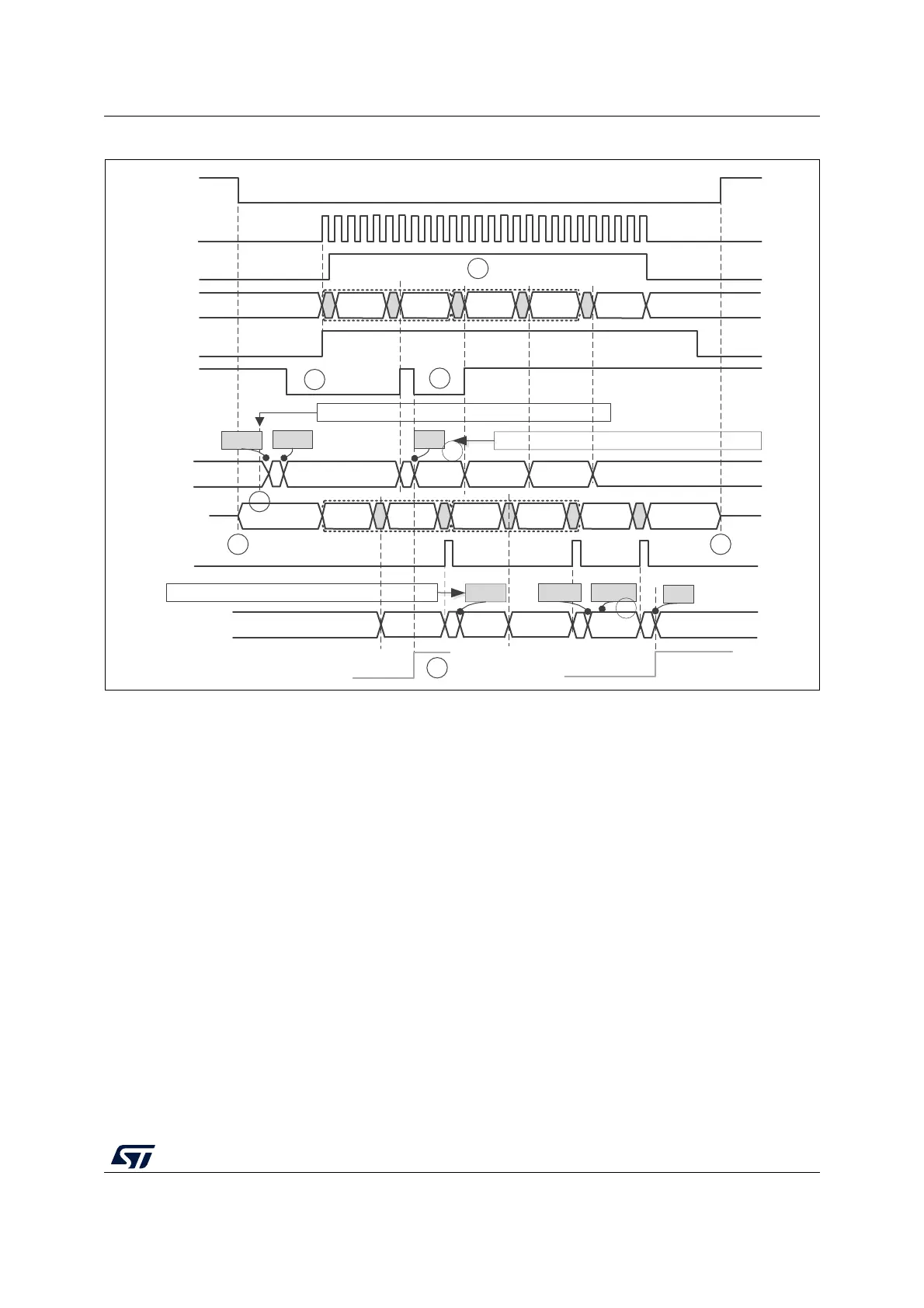

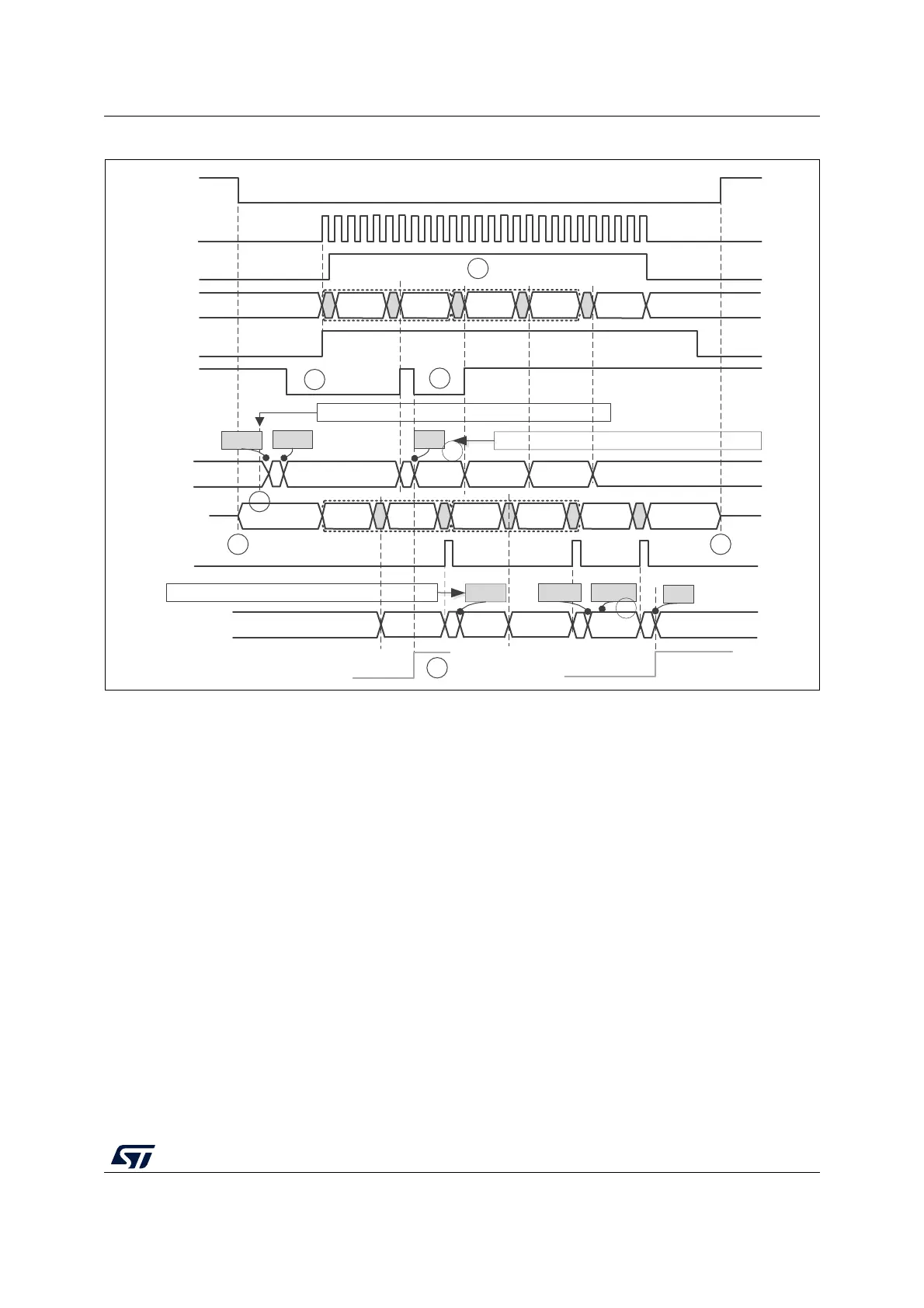

Figure 368. Master full-duplex communication in packed mode

Assumptions for master full-duplex communication in packed mode example:

• Data size = 5 bit

• Read/write FIFO is performed mostly by 16-bit access

• FRXTH=0

If DMA is used:

• Number of Tx frames to be transacted by DMA is set to 3

• Number of Rx frames to be transacted by DMA is set to 3

• PSIZE for both Tx and Rx DMA channel is set to 16-bit

• LDMA_TX=1 and LDMA_RX=1

See also : Communication diagrams on page 1155 for details about common assumptions

and notes.

4 3 2 1

10

NSS

SCK

BSY

MOSI

5

SPE

TXE

00

11

11 00

FTLVL

DTx1-2

DTx3-4

01

10

00

10

00 00

RXNE

DRx1-2

DRx3-4

DRx5

FRLVL

DMA Tx TICF

DMA Rx TICF

11

2

3

4

5

Enable Tx/Rx DMA or interrupts

DMA or software control at Tx events

DMA or software control at Rx events

10

DTx5

10

7

4 3 2 1

5

4 3 2 1

5

4 3 2 1

5

4 3 2 1

5

DTx1-2 DTx3-4 DTx5

5 4 3 2

1

5 4 3 2

1

5 4 3 2

1

5 4 3 2

1 1

5 4 3 2

MISO

DRx1-2

DRx3-4 DRx5

01

FRTHX=1

01

00

01

8

3

MSv32125V2

Loading...

Loading...