USB Type-C™ / USB Power Delivery interface (UCPD) RM0444

1332/1390 RM0444 Rev 5

38.7.4 UCPD control register (UCPD_CR)

Address offset: 0x00C

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is enabled (UCPDEN = 1).

Bits 31:29 Reserved, must be kept at reset value.

Bits 28:25 TRIM2_NG_CC3A0[3:0]: SW trim value for RP3A0 resistors on the CC2 line

Bits 24:20 TRIM2_NG_CC1A5[4:0]: SW trim value for RP1A5 resistors on the CC2 line

Bits 19:16 TRIM2_NG_CCRPD[3:0]: SW trim value for RPD resistors on the CC2 line

Bits 15:13 Reserved, must be kept at reset value.

Bits 12:9 TRIM1_NG_CC3A0[3:0]: SW trim value for RP3A0 resistors on the CC1 line

Bits 8:4 TRIM1_NG_CC1A5[4:0]: SW trim value for RP1A5 resistors on the CC1 line

Bits 3:0 TRIM1_NG_CCRPD[3:0]: SW trim value for RPD resistors on the CC1 line

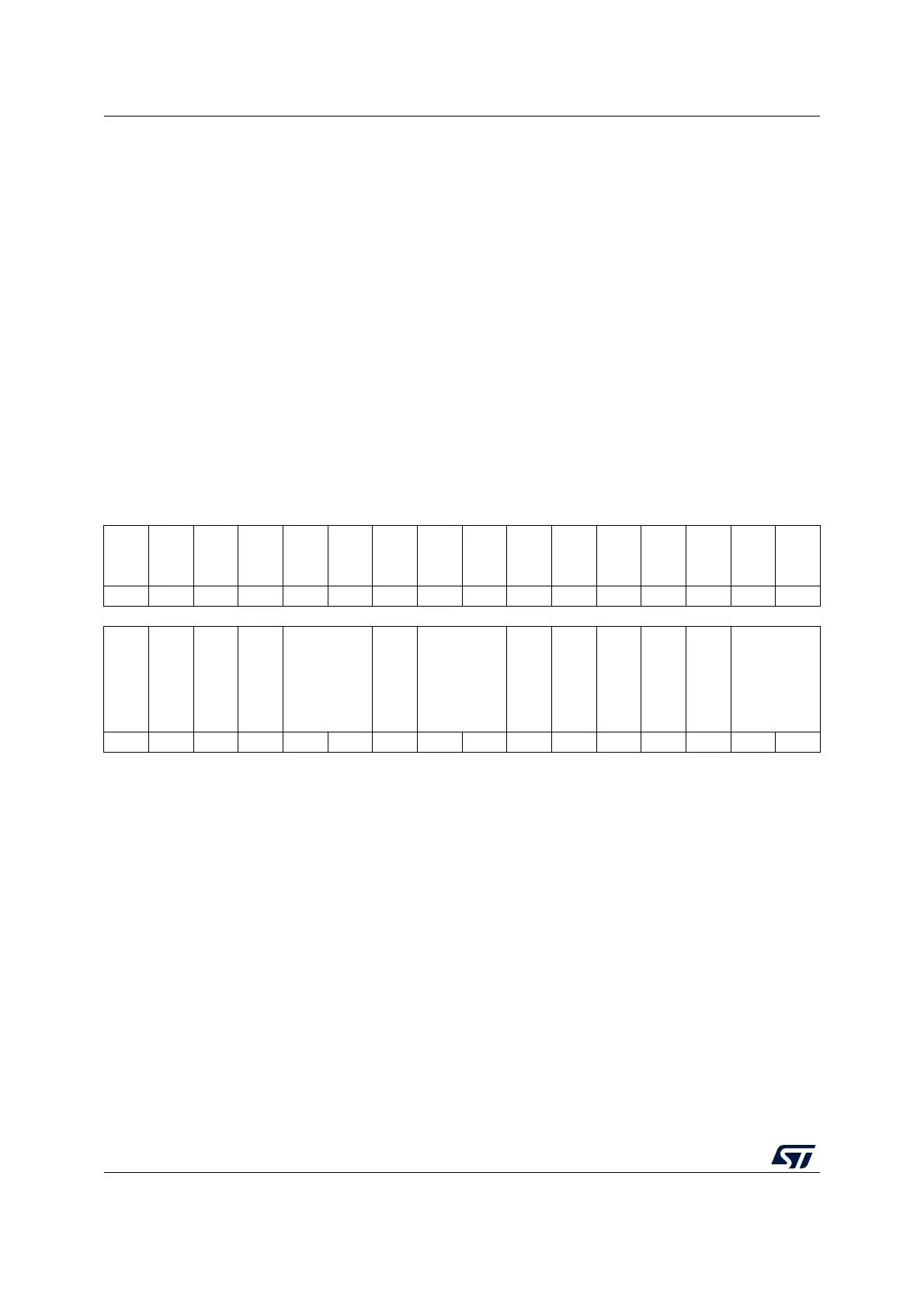

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

CC2TCDIS

CC1TCDIS

Res.

RDCH

FRSTX

FRSRXEN

rw rw rw rs rw

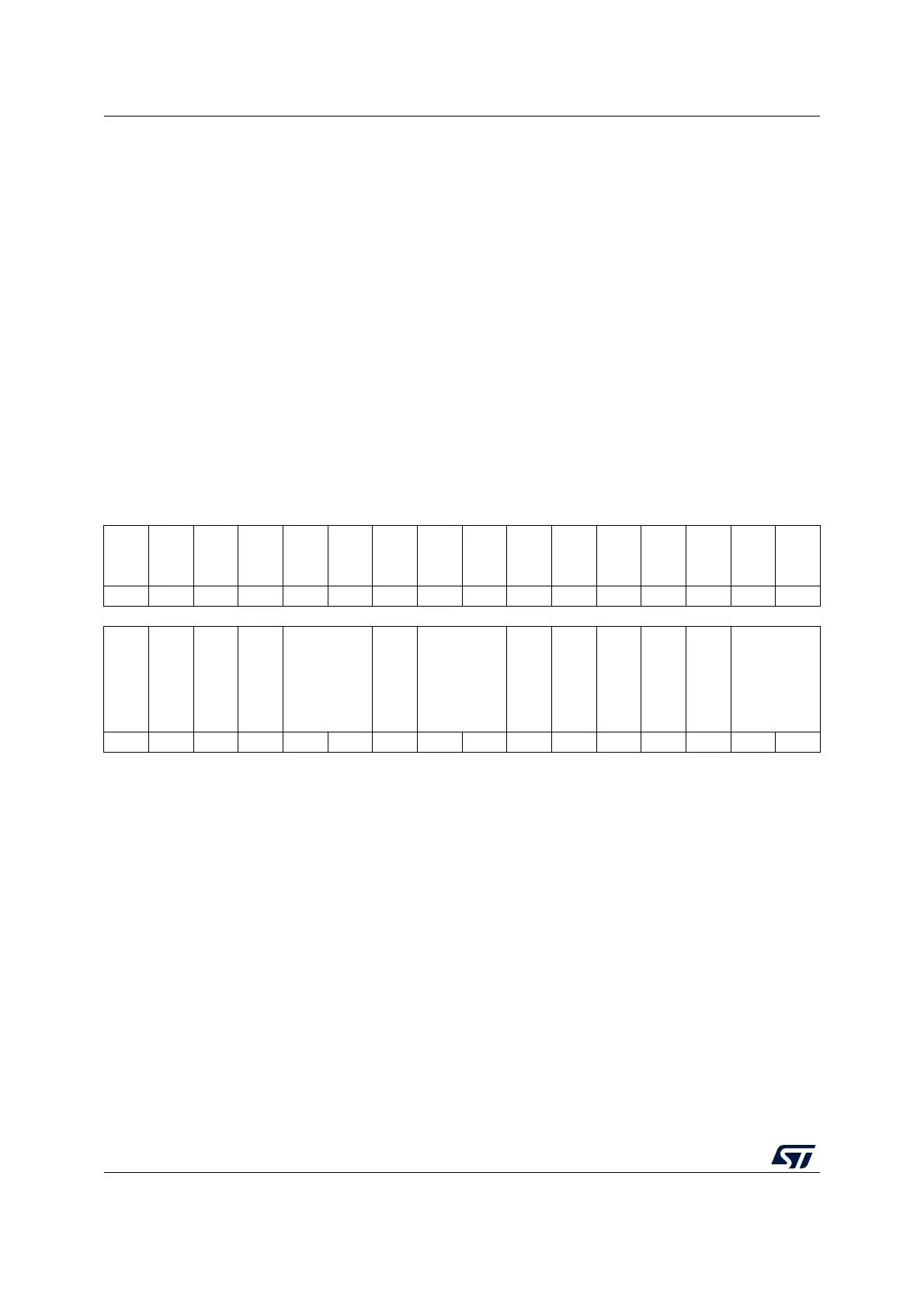

1514131211109876543210

DBATTEN

CC2VCONNEN

CC1VCONNEN

Res.

CCENABLE[1:0]

ANAMODE

ANASUBMODE[1:0]

PHYCCSEL

PHYRXEN

RXMODE

TXHRST

TXSEND

TXMODE[1:0]

rw rw rw rw rw rw rw rw rw rw rw rs rs rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bit 21 CC2TCDIS:CC2 Type-C detector disable

The bit disables the Type-C detector on the CC2 line.

0: Enable

1: Disable

When enabled, the Type-C detector for CC2 is configured through ANAMODE and

ANASUBMODE[1:0].

Bit 20 CC1TCDIS: CC1 Type-C detector disable

The bit disables the Type-C detector on the CC1 line.

0: Enable

1: Disable

When enabled, the Type-C detector for CC1 is configured through ANAMODE and

ANASUBMODE[1:0].

Bit 19 Reserved, must be kept at reset value.

Loading...

Loading...