Direct memory access controller (DMA) RM0444

290/1390 RM0444 Rev 5

10.6.3 DMA channel x configuration register (DMA_CCRx)

Address offset: 0x08 + 0x14 * (x - 1), (x = 1 to 7)

Reset value: 0x0000 0000

The register fields/bits MEM2MEM, PL[1:0], MSIZE[1:0], PSIZE[1:0], MINC, PINC, and DIR

are read-only when EN = 1.

The states of MEM2MEM and CIRC bits must not be both high at the same time.

Bit 17 CTCIF5: transfer complete flag clear for channel 5

Bit 16 CGIF5: global interrupt flag clear for channel 5

Bit 15 CTEIF4: transfer error flag clear for channel 4

Bit 14 CHTIF4: half transfer flag clear for channel 4

Bit 13 CTCIF4: transfer complete flag clear for channel 4

Bit 12 CGIF4: global interrupt flag clear for channel 4

Bit 11 CTEIF3: transfer error flag clear for channel 3

Bit 10 CHTIF3: half transfer flag clear for channel 3

Bit 9 CTCIF3: transfer complete flag clear for channel 3

Bit 8 CGIF3: global interrupt flag clear for channel 3

Bit 7 CTEIF2: transfer error flag clear for channel 2

Bit 6 CHTIF2: half transfer flag clear for channel 2

Bit 5 CTCIF2: transfer complete flag clear for channel 2

Bit 4 CGIF2: global interrupt flag clear for channel 2

Bit 3 CTEIF1: transfer error flag clear for channel 1

Bit 2 CHTIF1: half transfer flag clear for channel 1

Bit 1 CTCIF1: transfer complete flag clear for channel 1

Bit 0 CGIF1: global interrupt flag clear for channel 1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

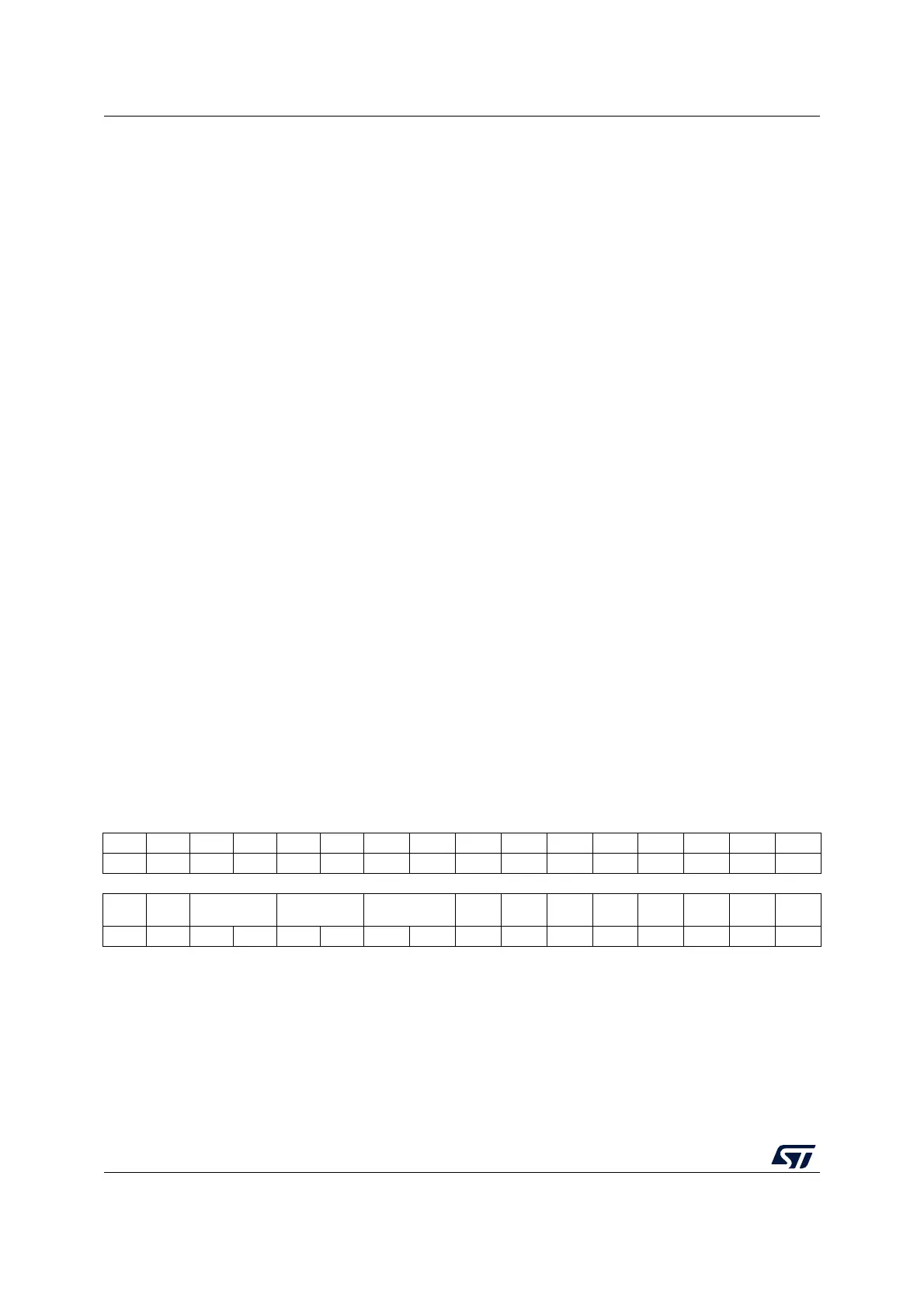

1514131211109876543210

Res.

MEM2

MEM

PL[1:0] MSIZE[1:0] PSIZE[1:0] MINC PINC CIRC DIR TEIE HTIE TCIE EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...