RM0444 Rev 5 517/1390

RM0444 AES hardware accelerator (AES)

522

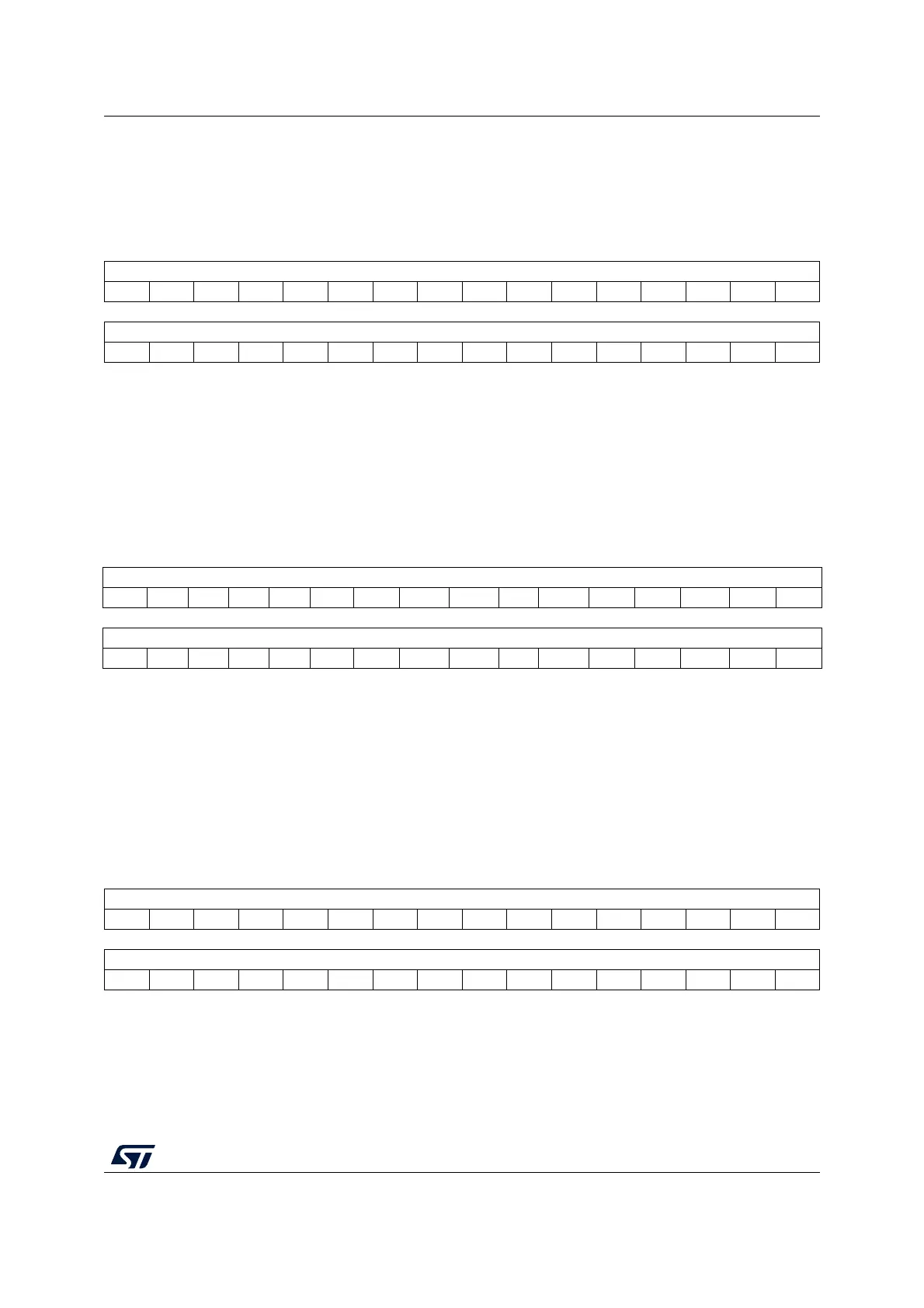

20.7.7 AES key register 2 (AES_KEYR2)

Address offset: 0x18

Reset value: 0x0000 0000

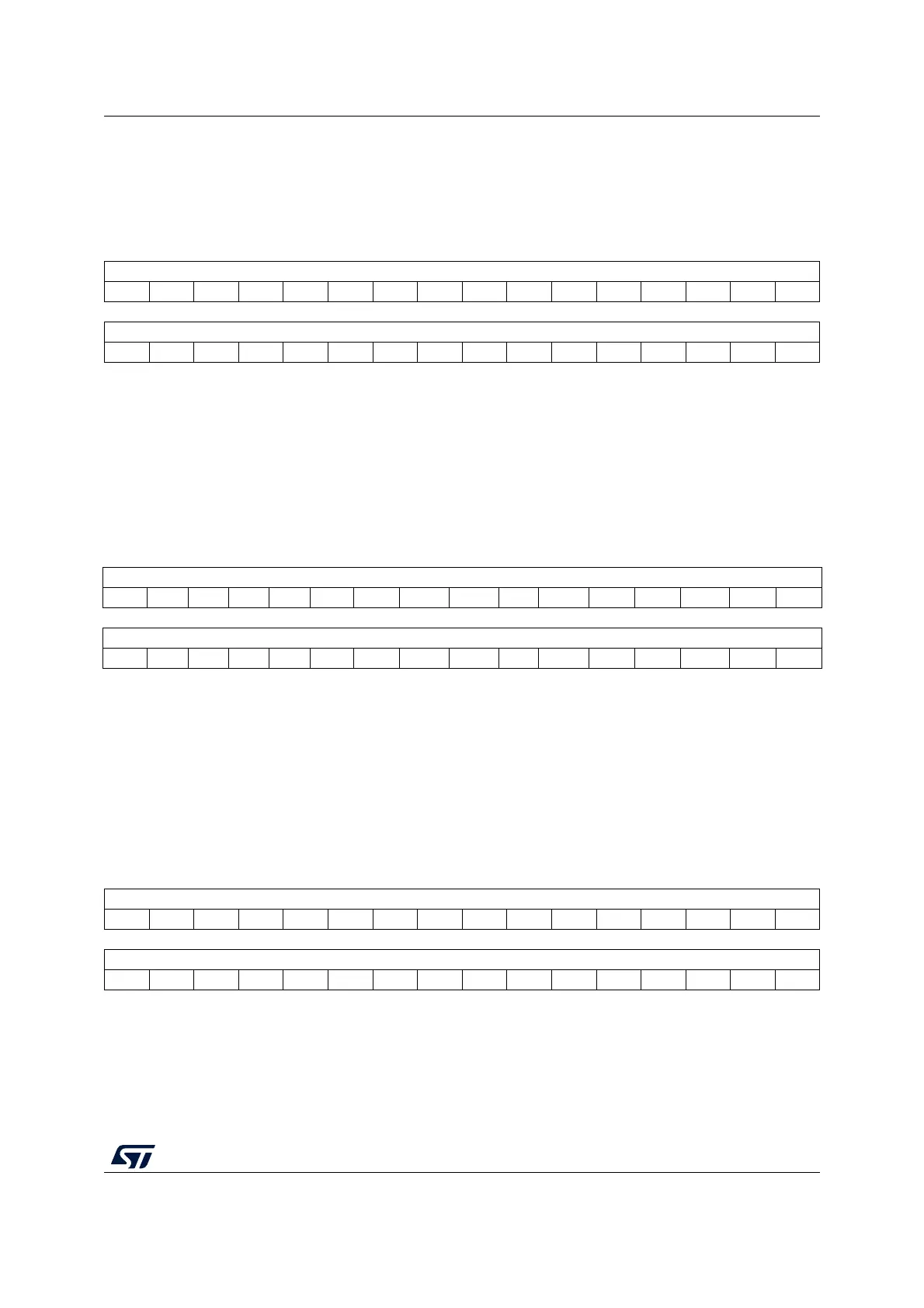

20.7.8 AES key register 3 (AES_KEYR3)

Address offset: 0x1C

Reset value: 0x0000 0000

20.7.9 AES initialization vector register 0 (AES_IVR0)

Address offset: 0x20

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEY[95:80]

wwwwwwwwwwwwwwww

1514131211109876543210

KEY[79:64]

wwwwwwwwwwwwwwww

Bits 31:0 KEY[95:64]: Cryptographic key, bits [95:64]

Refer to the AES_KEYR0 register for description of the KEY[255:0] bitfield.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEY[127:112]

wwwwwwww wwwwwwww

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

KEY[111:96]

wwwwwwww wwwwwwww

Bits 31:0 KEY[127:96]: Cryptographic key, bits [127:96]

Refer to the AES_KEYR0 register for description of the KEY[255:0] bitfield.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

IVI[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

IVI[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...