General-purpose timers (TIM15/TIM16/TIM17) RM0444

820/1390 RM0444 Rev 5

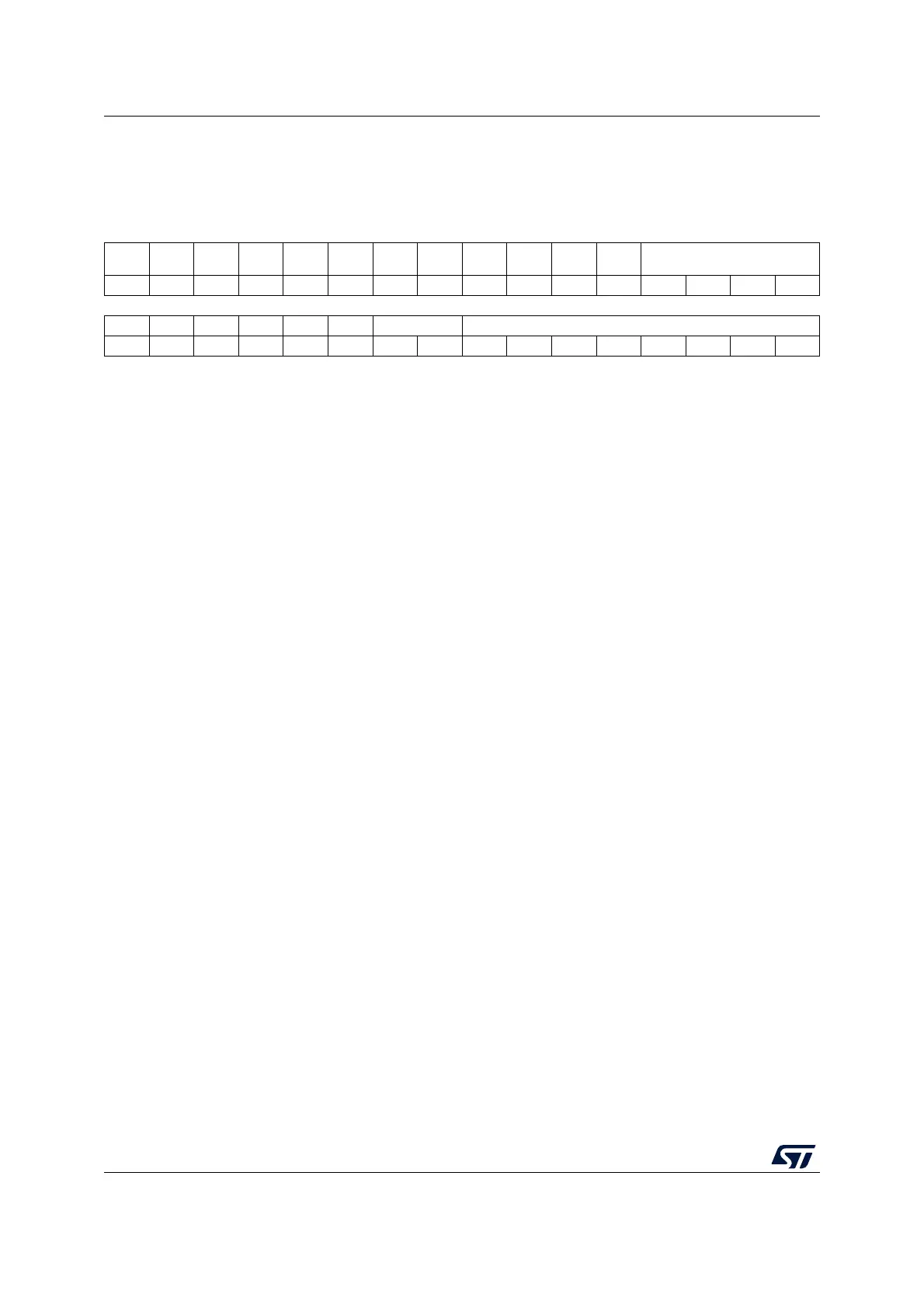

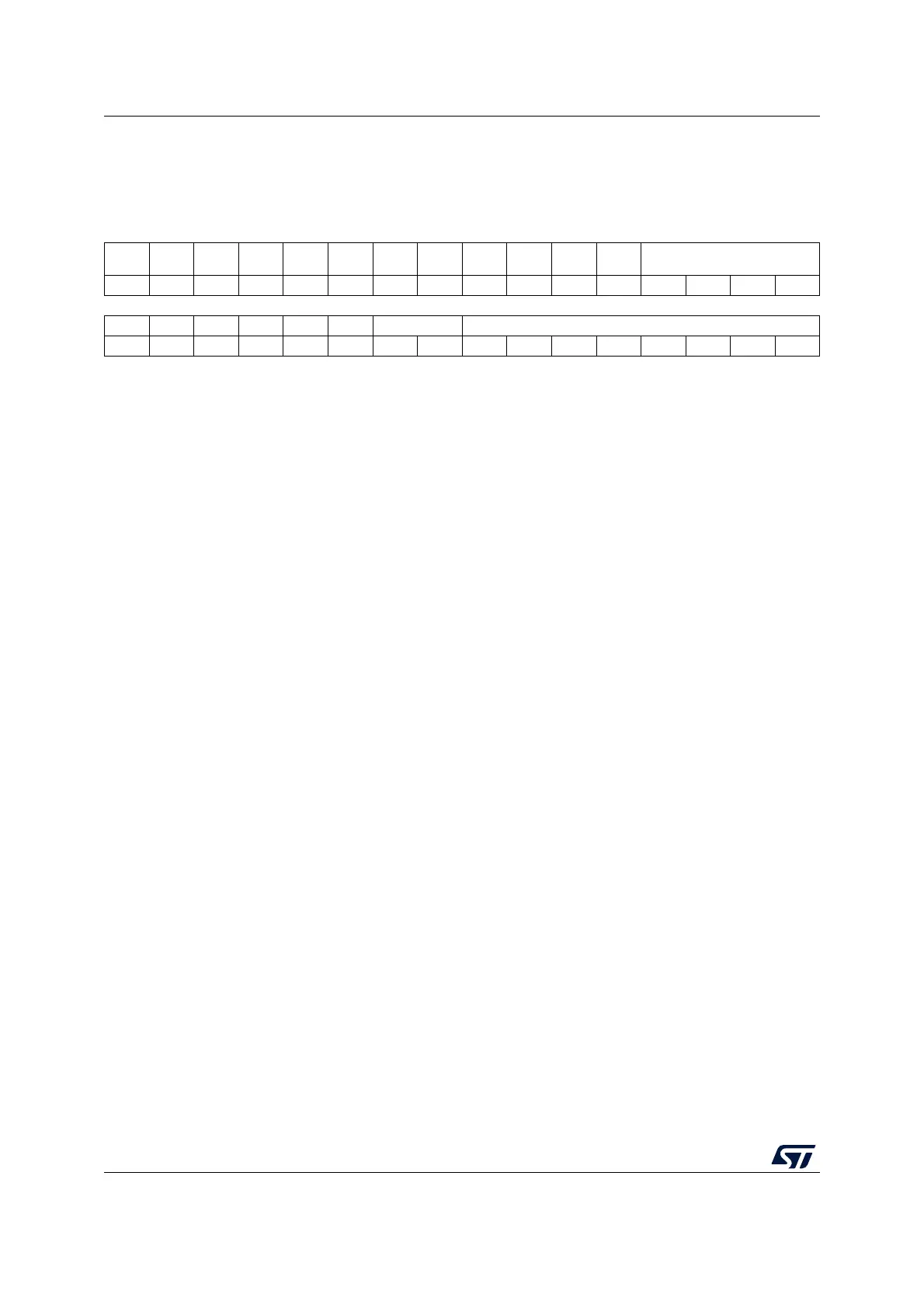

25.6.14 TIMx break and dead-time register (TIMx_BDTR)(x = 16 to 17)

Address offset: 0x44

Reset value: 0x0000 0000

Note: As the BKBID, BKDSRM, BKF[3:0], AOE, BKP, BKE, OSSI, OSSR and DTG[7:0] bits may

be write-locked depending on the LOCK configuration, it may be necessary to configure all

of them during the first write access to the TIMx_BDTR register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. BKBID Res.

BK

DSRM

Res. Res. Res. Res. Res. Res. BKF[3:0]

rw rw rw rw rw rw

1514131211109876543210

MOE AOE BKP BKE OSSR OSSI LOCK[1:0] DTG[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:29 Reserved, must be kept at reset value.

Bit 28 BKBID: Break Bidirectional

0: Break input BRK in input mode

1: Break input BRK in bidirectional mode

In the bidirectional mode (BKBID bit set to 1), the break input is configured both in input

mode and in open drain output mode. Any active break event asserts a low logic level on the

Break input to indicate an internal break event to external devices.

Note: This bit cannot be modified as long as LOCK level 1 has been programmed (LOCK bits

in TIMx_BDTR register).

Note: Any write operation to this bit takes a delay of 1 APB clock cycle to become effective.

Bit 27 Reserved, must be kept at reset value.

Bit 26 BKDSRM: Break Disarm

0: Break input BRK is armed

1: Break input BRK is disarmed

This bit is cleared by hardware when no break source is active.

The BKDSRM bit must be set by software to release the bidirectional output control (open-

drain output in Hi-Z state) and then be polled it until it is reset by hardware, indicating that the

fault condition has disappeared.

Note: Any write operation to this bit takes a delay of 1 APB clock cycle to become effective.

Loading...

Loading...