USB Type-C™ / USB Power Delivery interface (UCPD) RM0444

1328/1390 RM0444 Rev 5

It order to function correctly with the RCC, the clock request signal is activated (conditional

on WUPEN) when there is asynchronous activity on:

• Type-C voltage threshold detectors (coming from either CC line)

• Power Delivery receiver signal (from the selected CC line)

• FRS detection signal (from the selected CC line)

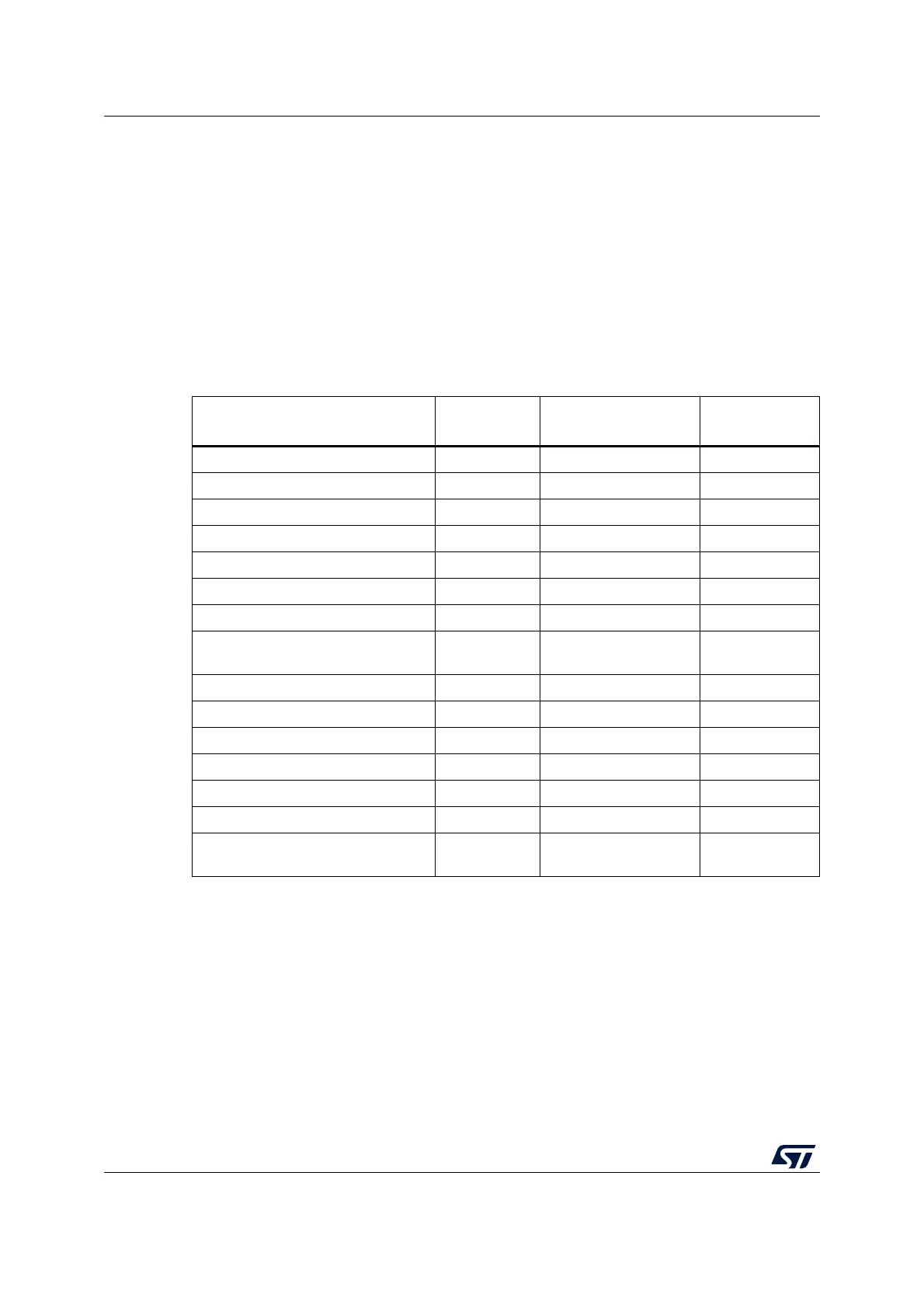

38.6 UCPD interrupts

The table below lists the UCPD event flags, with the associated flag clear bits and interrupt

enable bits.

When an interrupt from the UCPD is received, then the software has to check what is the

source of the interrupt by reading the UCPD_SR register.

Depending on which bit is at 1, the ISR must handle that condition and clear the bit by a

write to the appropriate bit of the UCPD_ICR register.

Table 240. UCPD interrupt requests

Interrupt event Event flag

Event flag/Interrupt

clearing method

Interrupt enable

control bit

FRS detection FRSEVT Set FRSEVTCF FRSEVTIE

Type C voltage level change on CC2 TYPECEVT2 Set TYPECEVT2CF TYPECEVT2IE

Type C voltage level change on CC1 TYPECEVT1 Set TYPECEVT1CF TYPECEVT1IE

Rx message received RXMSGEND Set RXMSGENDCF RXMSGENDIE

Rx data overflow RXOVR Set RXOVRCF RXOVR

Rx Hard Reset detected RXHRSTDET Set RXHRSTDETCF RXHRSTDETIE

Rx ordered set (4 K-codes) detected RXORDDET Set RXORDDETCF RXORDDETIE

Receive data register not empty RXNE

Read data in

UCPD_RXDR

RXNEIE

Tx data underrun TXUND Set TXUNDCF TXUNDIE

Hard Reset sent HRSTSENT Set HRSTSENTCF HRSTSENTIE

Hard Reset discarded HRSTDISC Set HRSTDISCCF HRSTDISCIE

Transmit message aborted TXMSGABT Set TXMSGABTCF TXMSGABTIE

Transmit message sent TXMSGSENT Set TXMSGSENTCF TXMSGSENTIE

Transmit message discarded TXMSGDISC Set TXMSGDISCCF TXMSGDISCIE

Transmit data required TXIS

Write data to the

UCPD_TXDR register

TXISIE

Loading...

Loading...