Power control (PWR) RM0444

148/1390 RM0444 Rev 5

4.4.5 Power status register 1 (PWR_SR1)

Address offset: 0x10

Reset value: 0x0000 0000. This register is not reset when exiting Standby modes and with

the PWRRST bit in the APB peripheral reset register 1 (RCC_APBRSTR1).

Access: 2 additional APB cycles are needed to read this register vs. a standard APB read.

Bit 5 WP6: WKUP6 wakeup pin polarity

WKUP6 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

Bit 4 WP5: WKUP5 wakeup pin polarity

WKUP5 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

Bit 3 WP4: WKUP4 wakeup pin polarity

WKUP4 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

Bit 1 WP3: WKUP3 wakeup pin polarity

WKUP3 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

Bit 1 WP2: WKUP2 wakeup pin polarity

WKUP2 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

Bit 0 WP1: WKUP1 wakeup pin polarity

WKUP1 external wakeup signal polarity (level or edge) triggering wakeup event:

0: High level or rising edge

1: Low level or falling edge

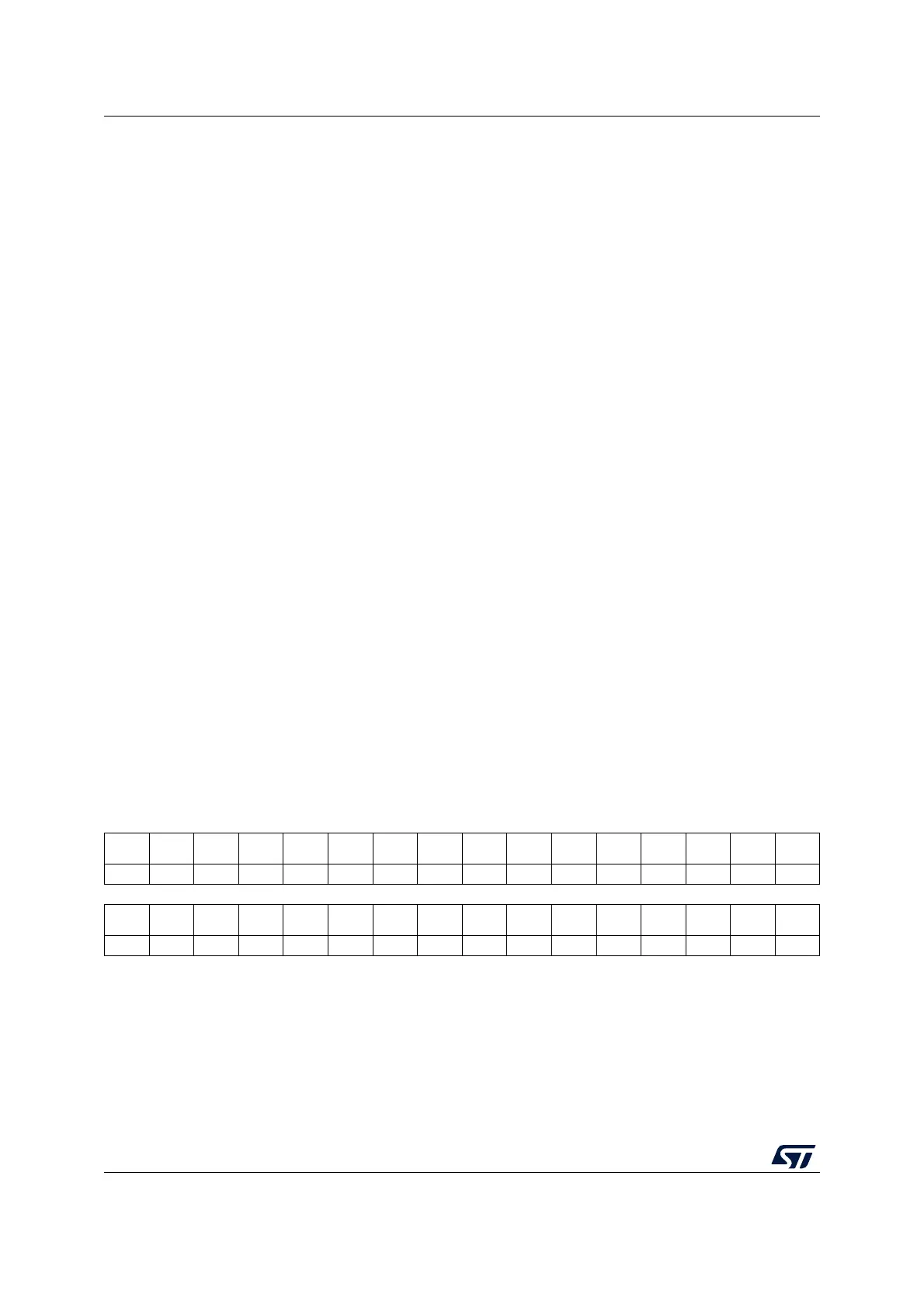

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

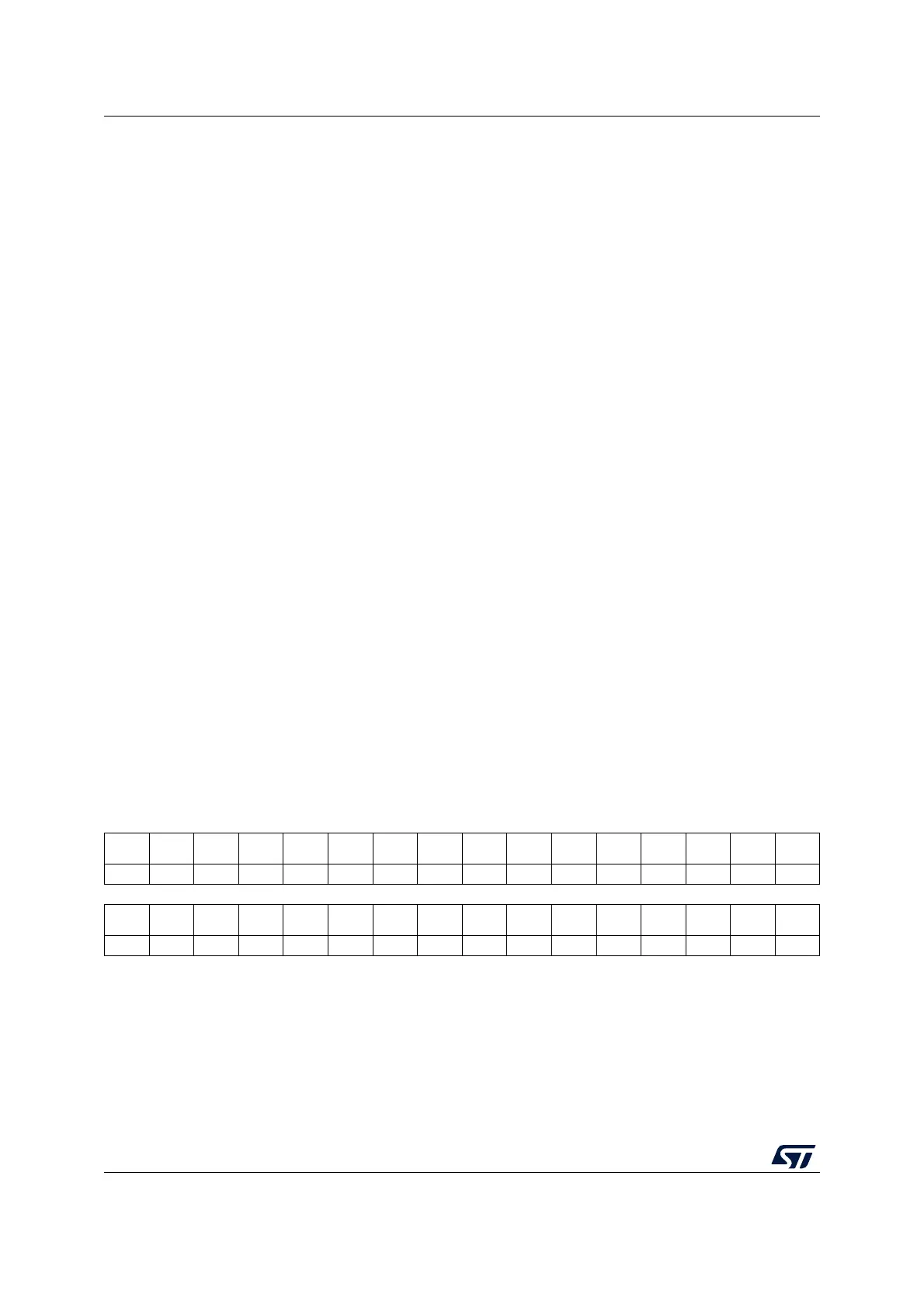

1514131211109876543210

WUFI Res. Res. Res. Res. Res. Res. SBF Res. Res. WUF6 WUF5 WUF4 WUF3 WUF2 WUF1

r r rrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 WUFI: Wakeup flag internal

This bit is set when a wakeup is detected on the internal wakeup line. It is cleared when all

internal wakeup sources are cleared.

Bits 14:9 Reserved, must be kept at reset value.

Loading...

Loading...