RM0444 Rev 5 1349/1390

RM0444 HDMI-CEC controller (CEC)

1364

All these blocks are made of a 8-bit payload - most significant bit is transmitted first -

followed by an end of message (EOM) bit and an acknowledge (ACK) bit.

The EOM bit is set in the last block of a message and kept reset in all others. In case a

message contains additional blocks after an EOM is indicated, those additional blocks must

be ignored. The EOM bit may be set in the header block to ‘ping’ other devices, to make

sure they are active.

The acknowledge bit is always set to high impedance by the initiator so that it can be driven

low either by the follower that has read its own address in the header, or by the follower that

needs to reject a broadcast message.

The header consists of the source logical address field, and the destination logical address

field. Note that the special address 0xF is used for broadcast messages.

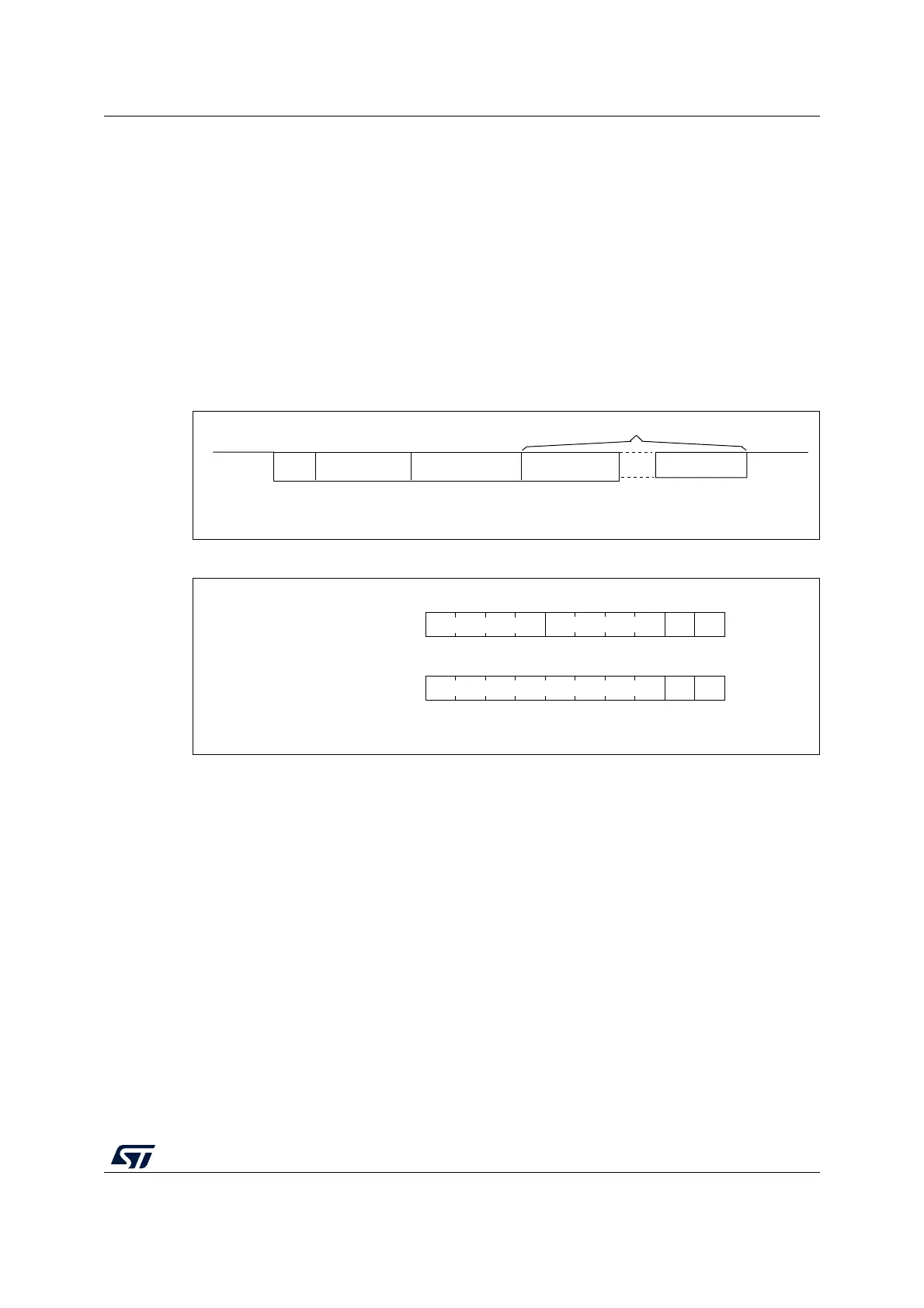

Figure 415. Message structure

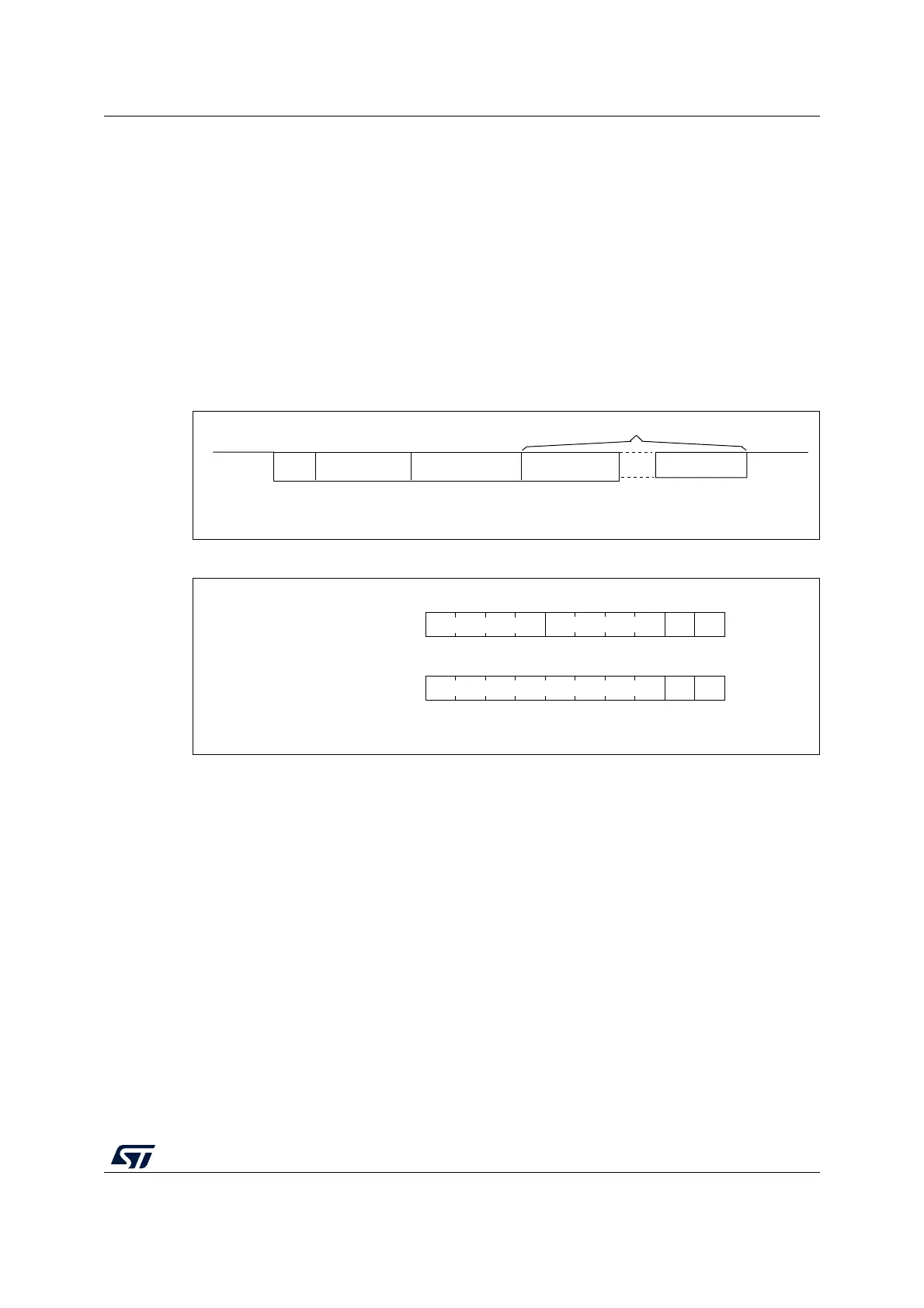

Figure 416. Blocks

39.3.4 Bit timing

The format of the start bit is unique and identifies the start of a message. It must be

validated by its low duration and its total duration.

All remaining data bits in the message, after the start bit, have consistent timing. The high-

to-low transition at the end of the data bit is the start of the next data bit except for the final

bit where the CEC line remains high.

MS31004V1

high

impedance

START

BIT

HEADER

OPCODE

0 to 14 operands

OPERAND

OPERAND

high

impedance

EOM ACK

0

DESTINATION[3:0]INITIATOR[3:0]

HEADER BLOCK

EOM ACK

0

DATA[7:0]

OPCODE/OPERAND BLOCK

MS31005V1

Loading...

Loading...