AES hardware accelerator (AES) RM0444

474/1390 RM0444 Rev 5

20.3 AES implementation

The devices have one AES peripheral.

20.4 AES functional description

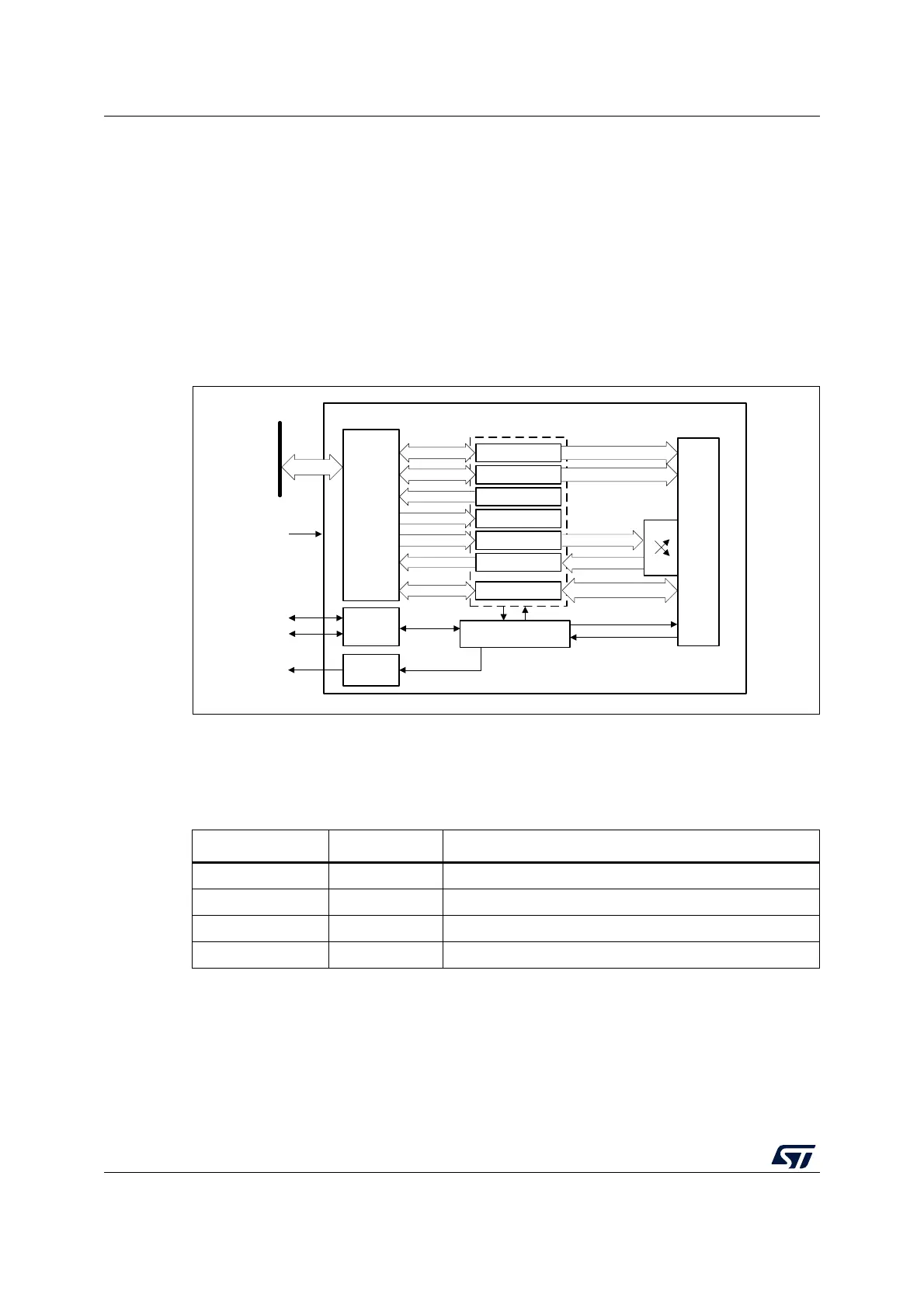

20.4.1 AES block diagram

Figure 75 shows the block diagram of AES.

Figure 75. AES block diagram

20.4.2 AES internal signals

Table 102 describes the user relevant internal signals interfacing the AES peripheral.

MSv42154V1

aes_hclk

Banked registers

DOUT

KEY

IVI

DIN

AES

key

control

status

IV, counter

data in

data out

aes_it

32-bit

AHB bus

aes_in_dma

AES_CR

AES_KEYRx

AES_SR

AES_IVRx

AES_DINR

AES_DOUTR

AES

Core

(AEA)

swap

AHB

interface

IRQ

interface

Control Logic

DMA

interface

aes_out_dma

32-bit

access

Save / Restore

AES_SUSPRx

Table 102. AES internal input/output signals

Signal name Signal type Description

aes_hclk Input AHB bus clock

aes_it Output AES interrupt request

aes_in_dma Input/Output Input DMA single request/acknowledge

aes_out_dma Input/Output Output DMA single request/acknowledge

Loading...

Loading...