RM0444 Rev 5 149/1390

RM0444 Power control (PWR)

159

4.4.6 Power status register 2 (PWR_SR2)

Address offset: 0x14

Reset value: 0x0000 0000. This register is partially reset when exiting Standby/Shutdown

modes.

Bit 8 SBF: Standby flag

This bit is set by hardware when the device enters Standby mode and is cleared by setting

the CSBF bit in the PWR_SCR register, or by a power-on reset. It is not cleared by the

system reset.

0: The device did not enter Standby mode

1: The device entered Standby mode

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 WUF6: Wakeup flag 6

This bit is set when a wakeup event is detected on WKUP6 wakeup pin. It is cleared by

writing 1 in the CWUF6 bit of the PWR_SCR register.

Bit 4 WUF5: Wakeup flag 5

This bit is set when a wakeup event is detected on WKUP5 wakeup pin. It is cleared by

writing 1 in the CWUF5 bit of the PWR_SCR register.

Bit 3 WUF4: Wakeup flag 4

This bit is set when a wakeup event is detected on WKUP4 wakeup pin. It is cleared by

writing 1 in the CWUF4 bit of the PWR_SCR register.

Bit 2 WUF3: Wakeup flag 3

This bit is set when a wakeup event is detected on WKUP3 wakeup pin. It is cleared by

writing 1 in the CWUF3 bit of the PWR_SCR register.

Bit 1 WUF2: Wakeup flag 2

This bit is set when a wakeup event is detected on WKUP2 wakeup pin. It is cleared by

writing 1 in the CWUF2 bit of the PWR_SCR register.

Bit 0 WUF1: Wakeup flag 1

This bit is set when a wakeup event is detected on WKUP1 wakeup pin. It is cleared by

writing 1 in the CWUF1 bit of the PWR_SCR register.

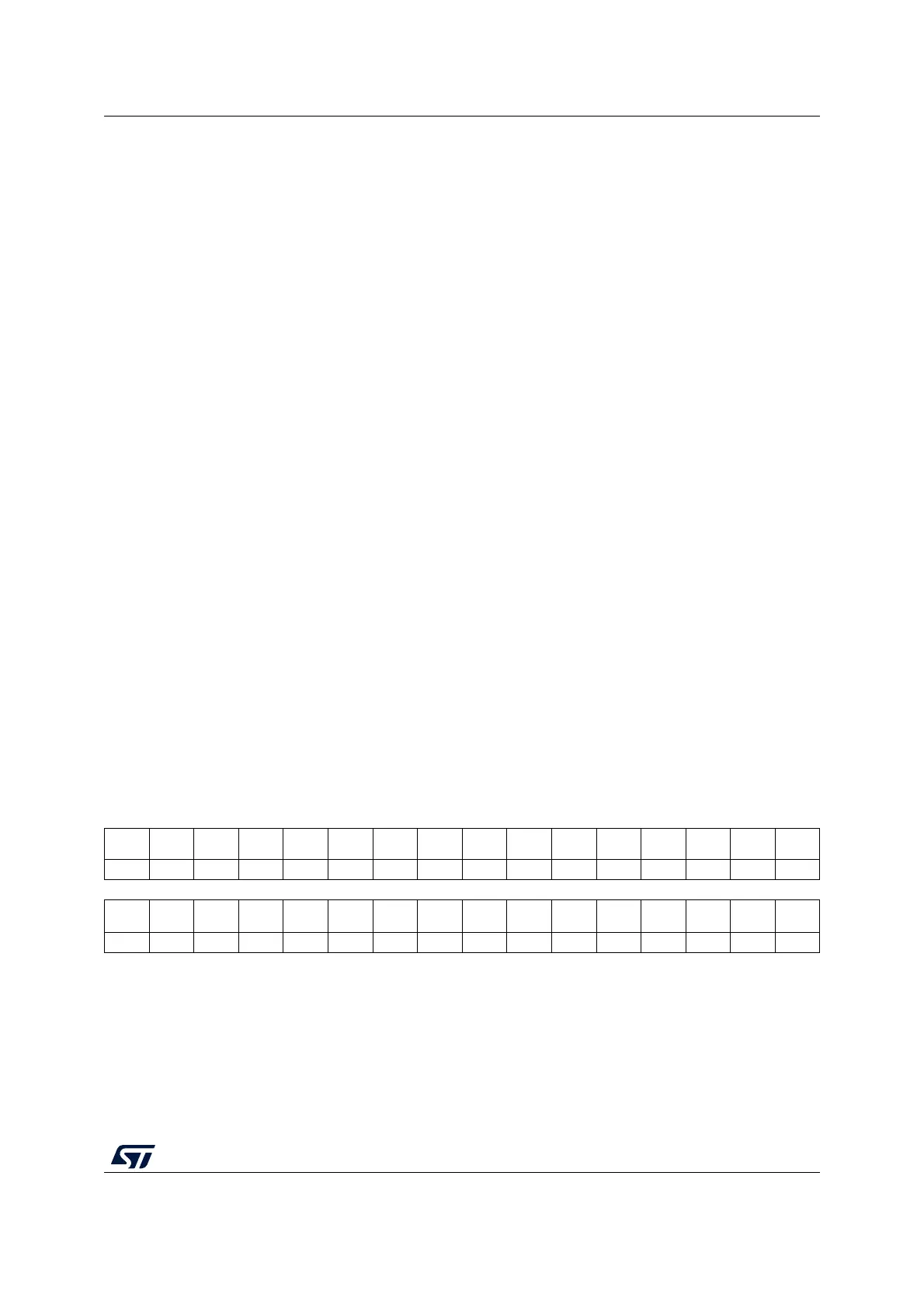

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

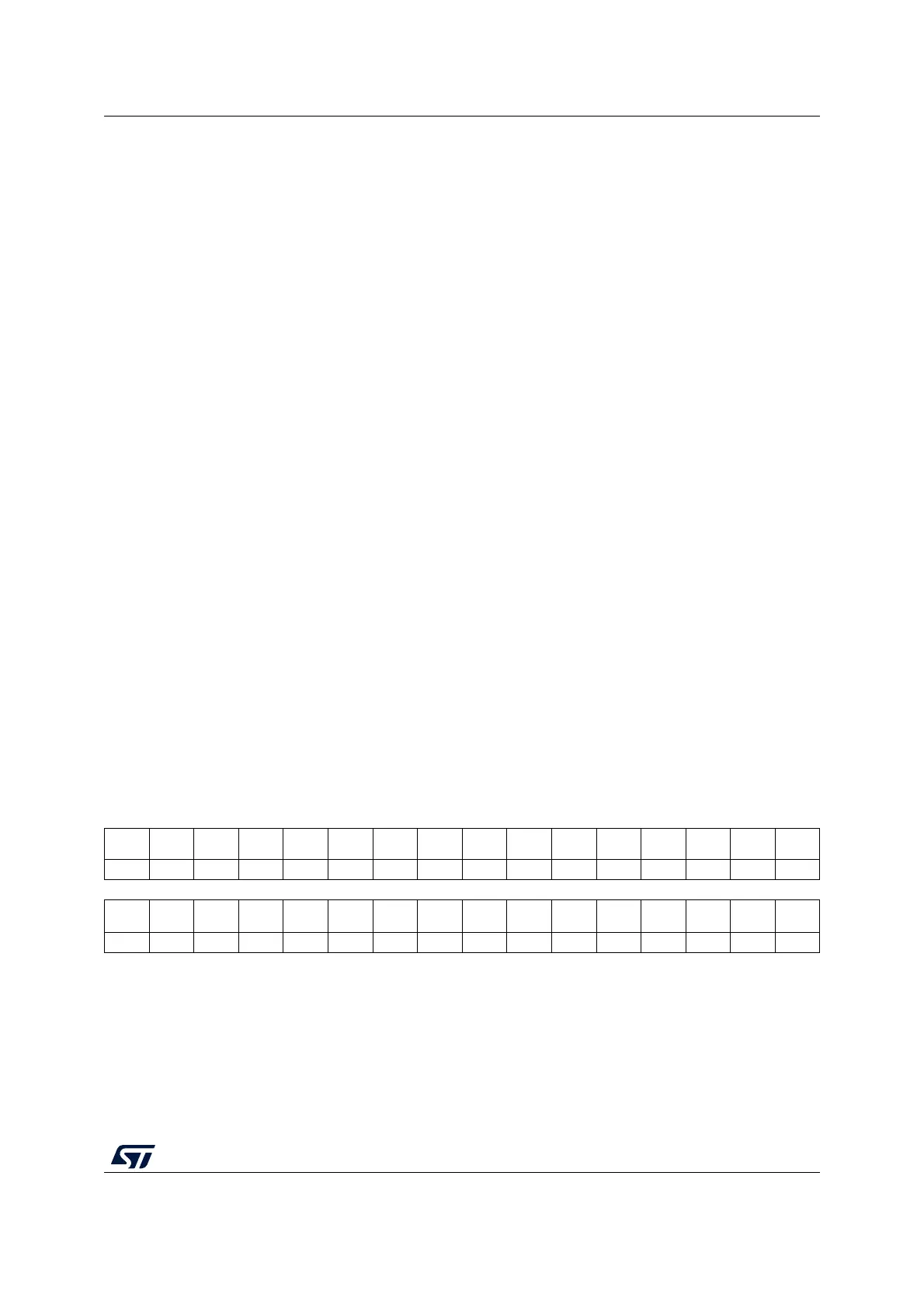

1514131211109876543210

PVMO

DAC

Res. Res.

PVMO

USB

PVDO VOSF

REGLP

F

REGLP

S

FLASH

_RDY

Res. Res. Res. Res. Res. Res. Res.

r rrrrrr

Loading...

Loading...