General-purpose timers (TIM14) RM0444

736/1390 RM0444 Rev 5

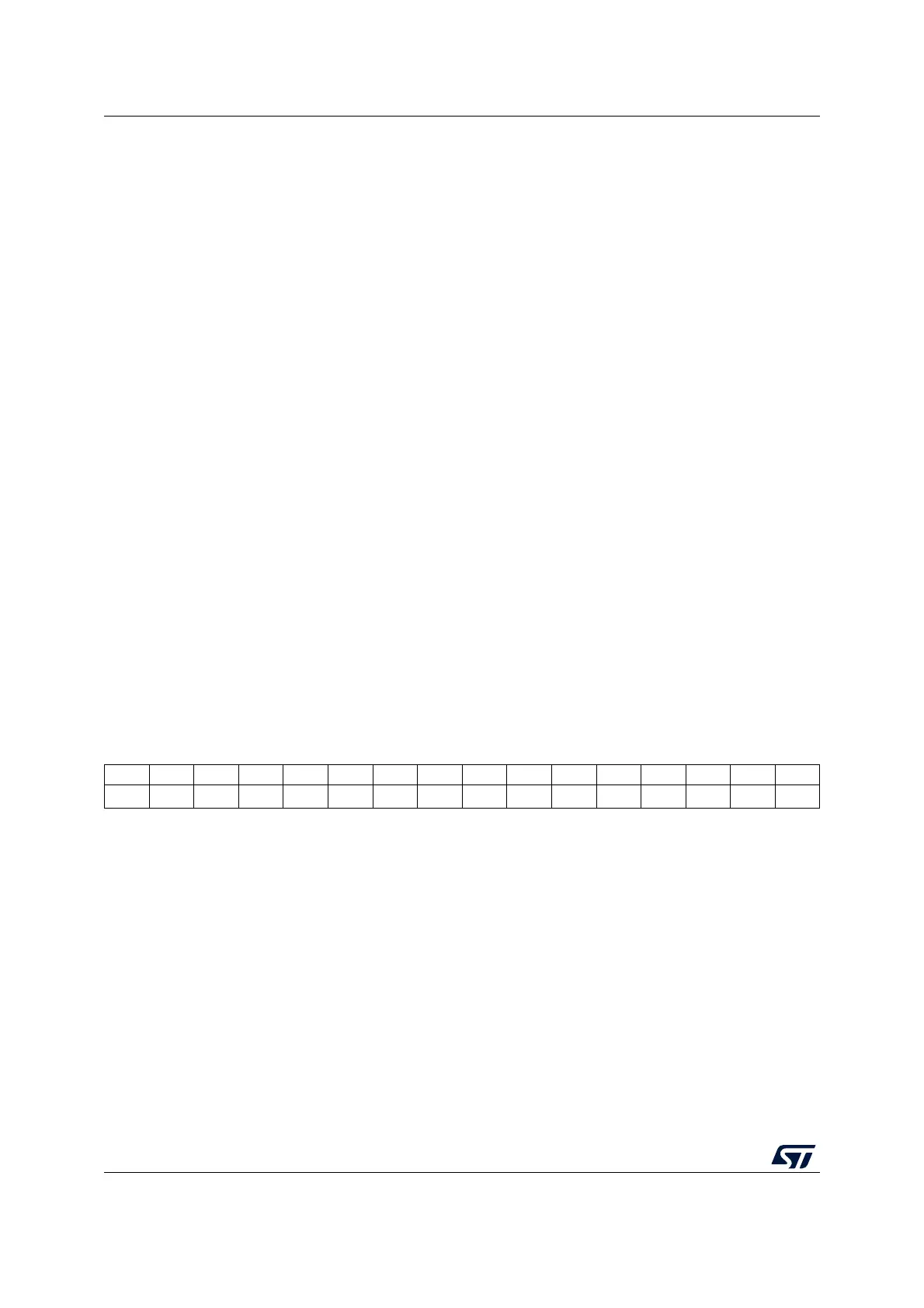

24.4.7 TIM14 capture/compare enable register (TIM14_CCER)

Address offset: 0x20

Reset value: 0x0000

Bit 3 OC1PE: Output compare 1 preload enable

0: Preload register on TIMx_CCR1 disabled. TIMx_CCR1 can be written at anytime, the

new value is taken in account immediately.

1: Preload register on TIMx_CCR1 enabled. Read/Write operations access the preload

register. TIMx_CCR1 preload value is loaded in the active register at each update event.

Note: The PWM mode can be used without validating the preload register only in one pulse

mode (OPM bit set in TIMx_CR1 register). Else the behavior is not guaranteed.

Bit 2 OC1FE: Output compare 1 fast enable

This bit decreases the latency between a trigger event and a transition on the timer output. It

must be used in one-pulse mode (OPM bit set in TIMx_CR1 register), to have the output

pulse starting as soon as possible after the starting trigger.

0: CC1 behaves normally depending on counter and CCR1 values even when the trigger is

ON. The minimum delay to activate CC1 output when an edge occurs on the trigger input

is 5 clock cycles.

1: An active edge on the trigger input acts like a compare match on CC1 output. OC is then

set to the compare level independently of the result of the comparison. Delay to sample

the trigger input and to activate CC1 output is reduced to 3 clock cycles. OC1FE acts only

if the channel is configured in PWM1 or PWM2 mode.

Bits 1:0 CC1S[1:0]: Capture/Compare 1 selection

This bit-field defines the direction of the channel (input/output) as well as the used input.

00: CC1 channel is configured as output.

01: CC1 channel is configured as input, IC1 is mapped on TI1.

10: Reserved.

11: Reserved.

Note: CC1S bits are writable only when the channel is OFF (CC1E = 0 in TIMx_CCER).

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CC1NP Res. CC1P CC1E

rw rw rw

Bits 15:4 Reserved, must be kept at reset value.

Bit 3 CC1NP: Capture/Compare 1 complementary output Polarity.

CC1 channel configured as output: CC1NP must be kept cleared.

CC1 channel configured as input: CC1NP bit is used in conjunction with CC1P to define

TI1FP1 polarity (refer to CC1P description).

Loading...

Loading...