FD controller area network (FDCAN) RM0444

1250/1390 RM0444 Rev 5

36.4.25 FDCAN Rx FIFO 1 acknowledge register (FDCAN_RXF1A)

Address offset: 0x009C

Reset value: 0x0000 0000

36.4.26 FDCAN Tx buffer configuration register (FDCAN_TXBC)

Address offset: 0x00C0

Reset value: 0x0000 0000

Bits 17:16 F1PI[1:0]: Rx FIFO 1 put index

Rx FIFO 1 write index pointer, range 0 to 2.

Bits 15:10 Reserved, must be kept at reset value.

Bits 9:8 F1GI[1:0]: Rx FIFO 1 get index

Rx FIFO 1 read index pointer, range 0 to 2.

Bits 7:4 Reserved, must be kept at reset value.

Bits 3:0 F1FL[3:0]: Rx FIFO 1 fill level

Number of elements stored in Rx FIFO 1, range 0 to 3.

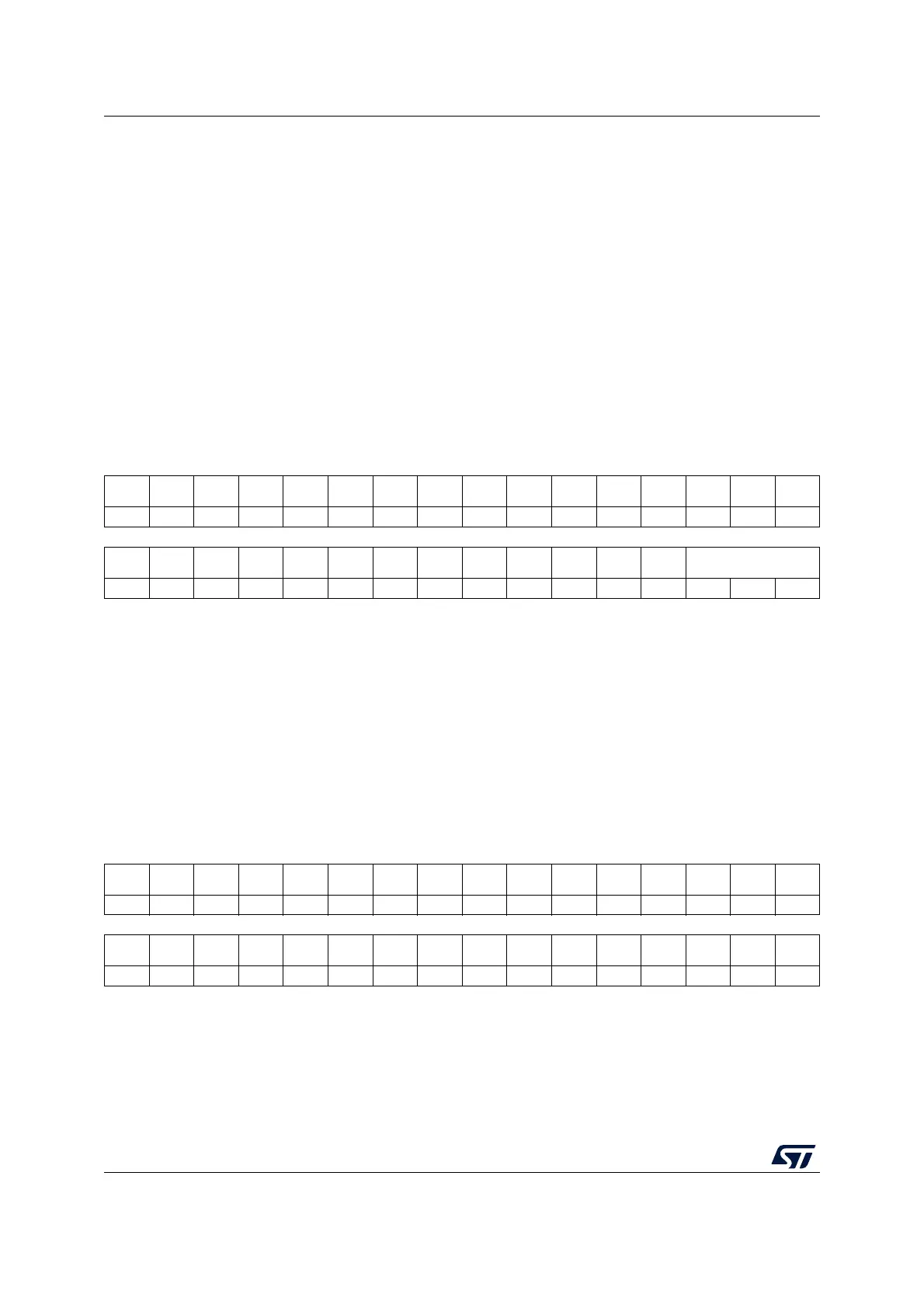

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. F1AI[2:0]

rw rw rw

Bits 31:3 Reserved, must be kept at reset value.

Bits 2:0 F1AI[2:0]: Rx FIFO 1 acknowledge index

After the Host has read a message or a sequence of messages from Rx FIFO 1 it has to write

the buffer index of the last element read from Rx FIFO 1 to F1AI. This sets the Rx FIFO 1 get

index RXF1S[F1GI] to F1AI + 1 and update the FIFO 1 Fill Level RXF1S[F1FL].

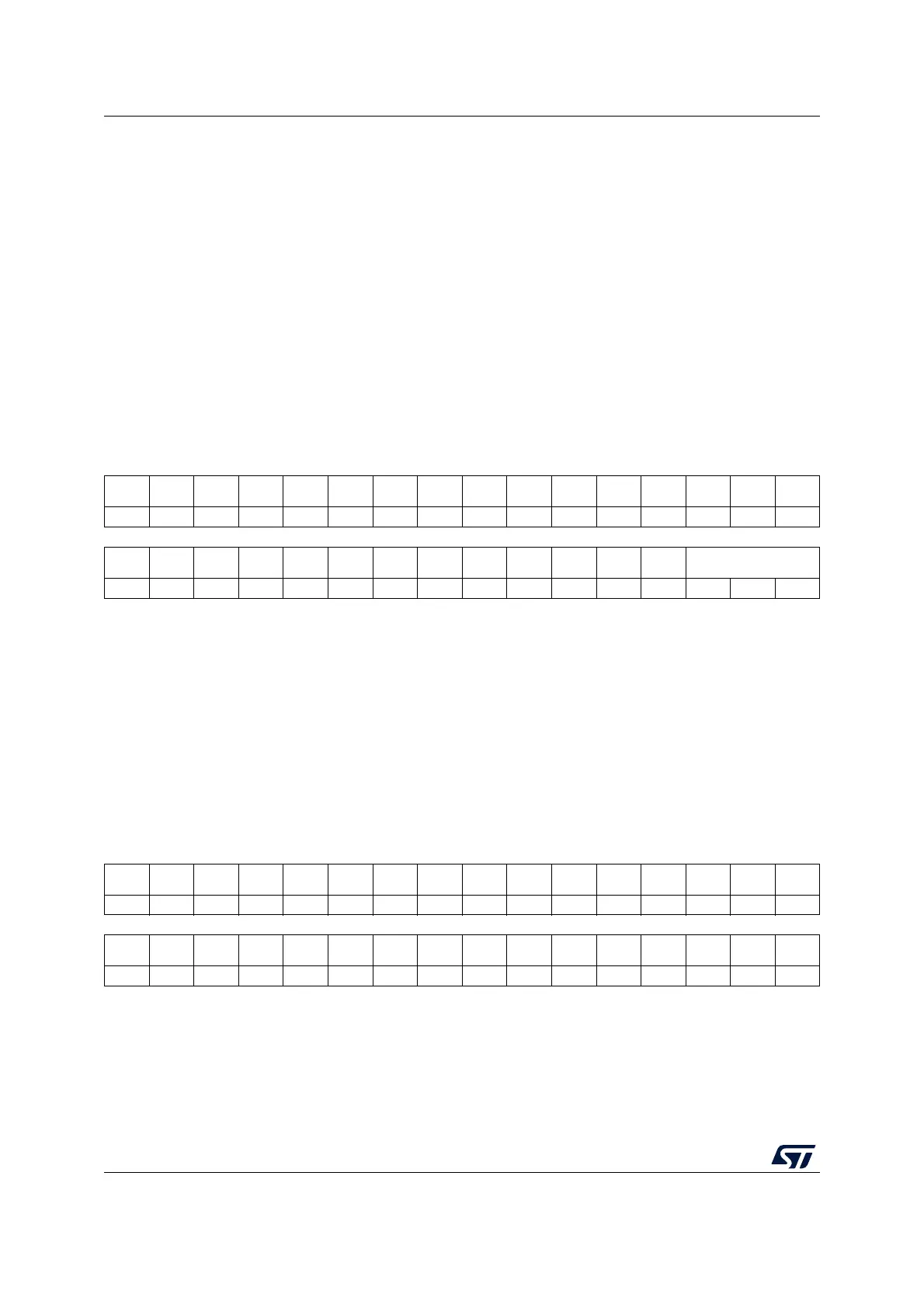

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. TFQM Res. Res. Res. Res. Res. Res. Res. Res.

rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

Loading...

Loading...