Comparator (COMP) RM0444

448/1390 RM0444 Rev 5

18.3.3 COMP reset and clocks

The COMP clock provided by the clock controller is synchronous with the APB2 clock.

There is no clock enable control bit provided in the RCC controller. Reset and clock enable

bits are common for COMP and SYSCFG.

Important: The polarity selection logic and the output redirection to the port works

independently from the APB2 clock. This allows the comparator to work even in Stop mode.

18.3.4 Comparator LOCK mechanism

The comparators can be used for safety purposes, such as over-current or thermal

protection. For applications having specific functional safety requirements, it is necessary to

insure that the comparator programming cannot be altered in case of spurious register

access or program counter corruption.

For this purpose, the comparator control and status registers can be write-protected (read-

only).

Once the programming is completed, the COMPx LOCK bit can be set to 1. This causes the

whole register to become read-only, including the COMPx LOCK bit.

The write protection can only be reset by a MCU reset.

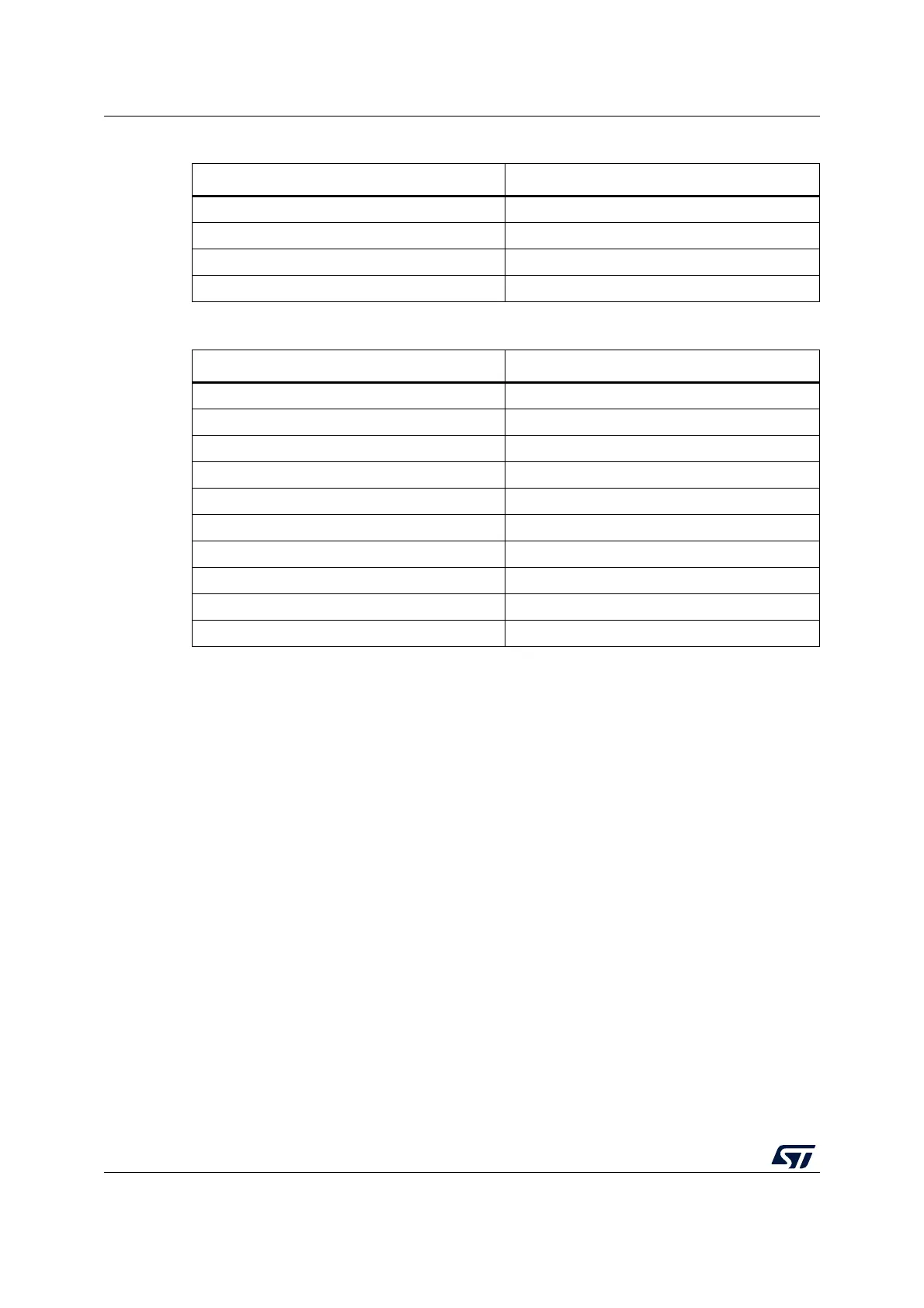

Table 94. COMP3 non-inverting input assignment

COMP3_INP COMP3_INPSEL[1:0]

PB0 00

PC1 01

PE7 10

Open 11

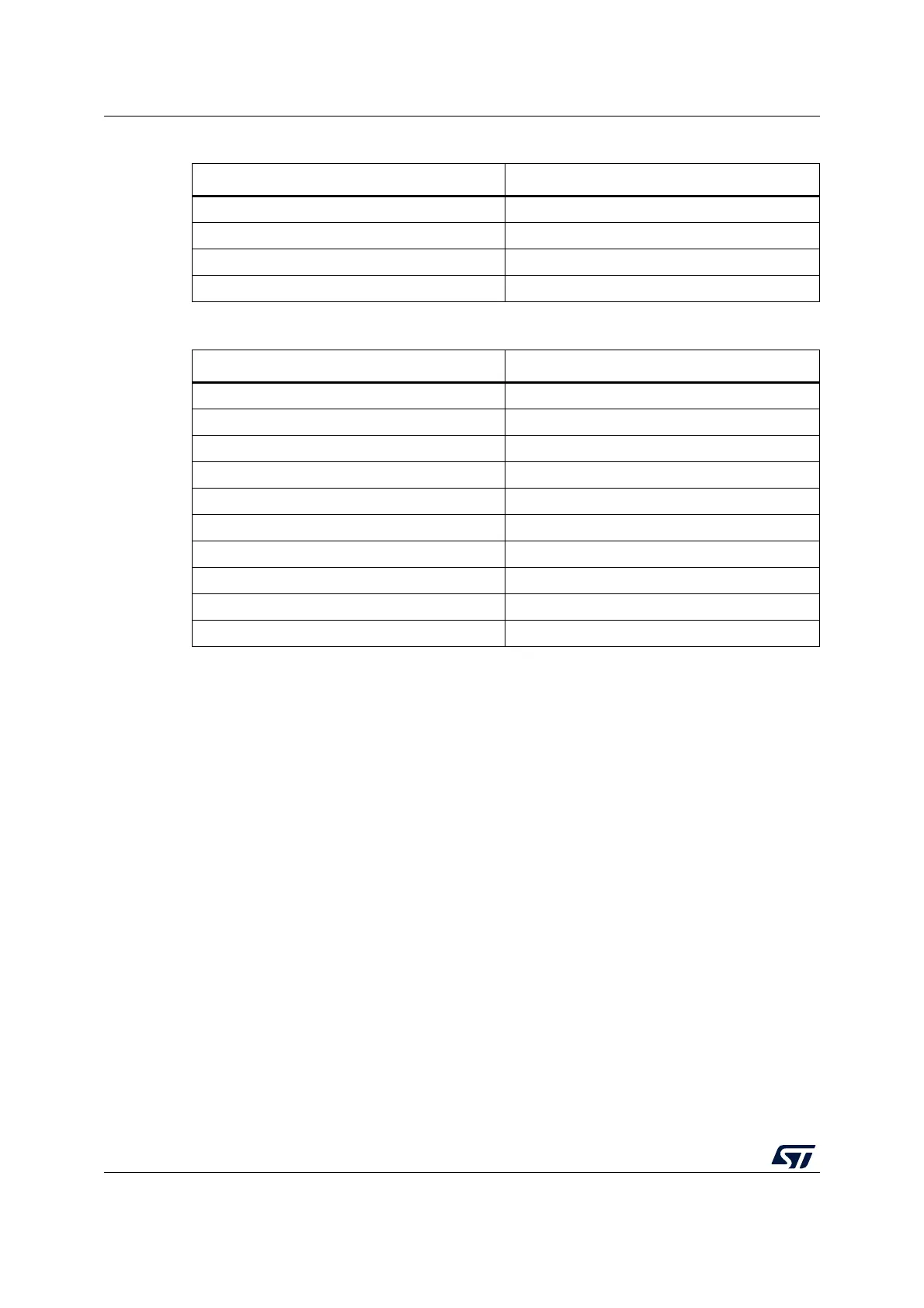

Table 95. COMP3 inverting input assignment

COMP3_INM COMP3_INMSEL[3:0]

¼ V

REFINT

0000

½ V

REFINT

0001

¾ V

REFINT

0010

V

REFINT

0011

DAC Channel1 0100

DAC Channel2 0101

PB2 0110

PC0 0111

PE8 1000

¼ V

REFINT

> 1000

Loading...

Loading...