Debug support (DBG) RM0444

1374/1390 RM0444 Rev 5

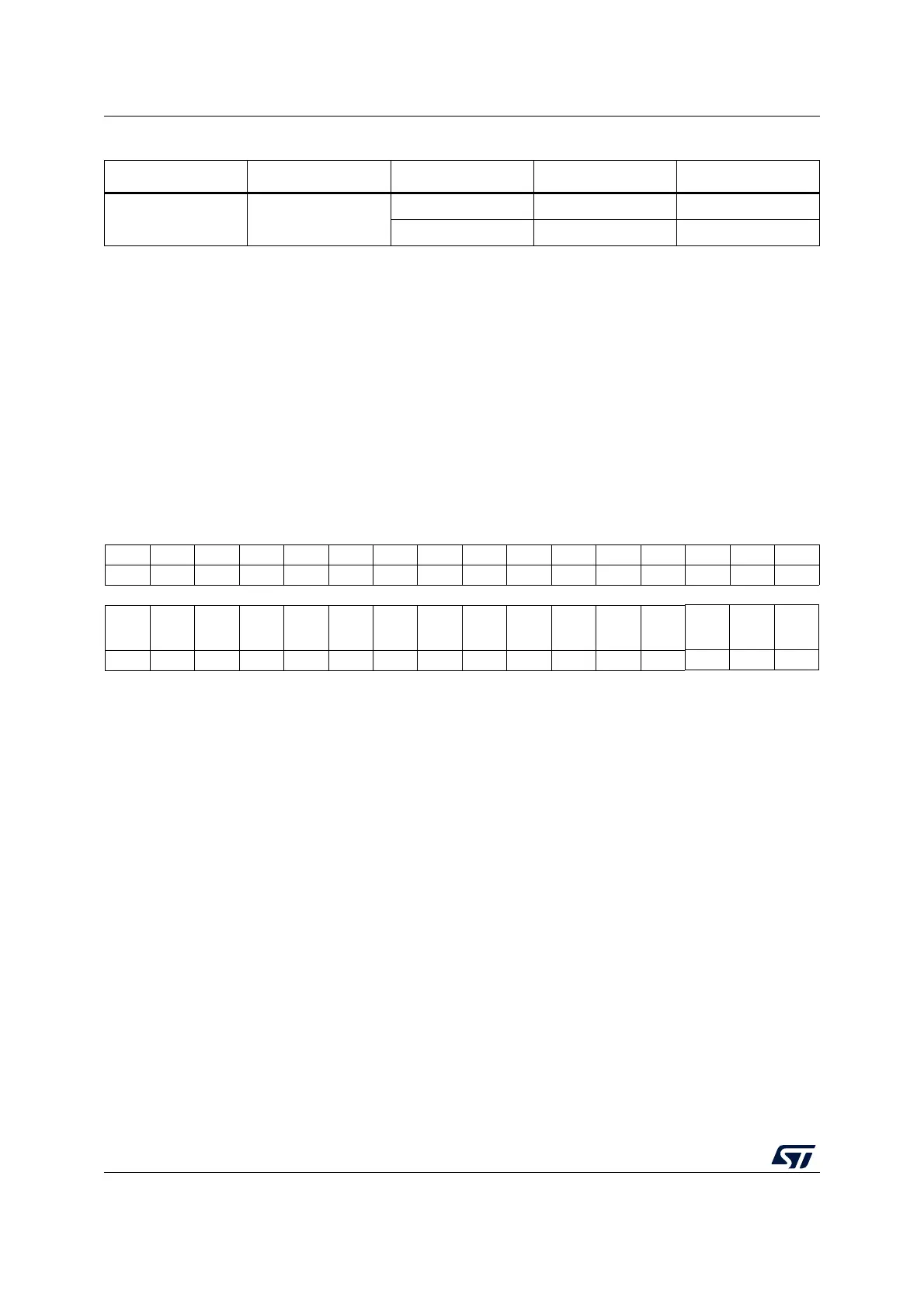

40.10.2 DBG configuration register (DBG_CR)

This register configures the low-power modes of the MCU under debug.

It is asynchronously reset by the POR (and not the system reset). It can be written by the

debugger under system reset.

If the debugger host does not support this feature, it is still possible for the user software to

write to this register.

Address offset: 0x04

POR Reset: 0x0000 0000 (not reset by system reset)

Only 32-bit access supported

40.10.3 DBG APB freeze register 1 (DBG_APB_FZ1)

This register configures the clocking of timers, RTC, IWDG, WWDG, and I2C SMBUS

peripherals of the MCU under debug:

STM32G031xx and

STM32G041xx

0x466

A 1.0 0x1000

Z 1.1 0x1001

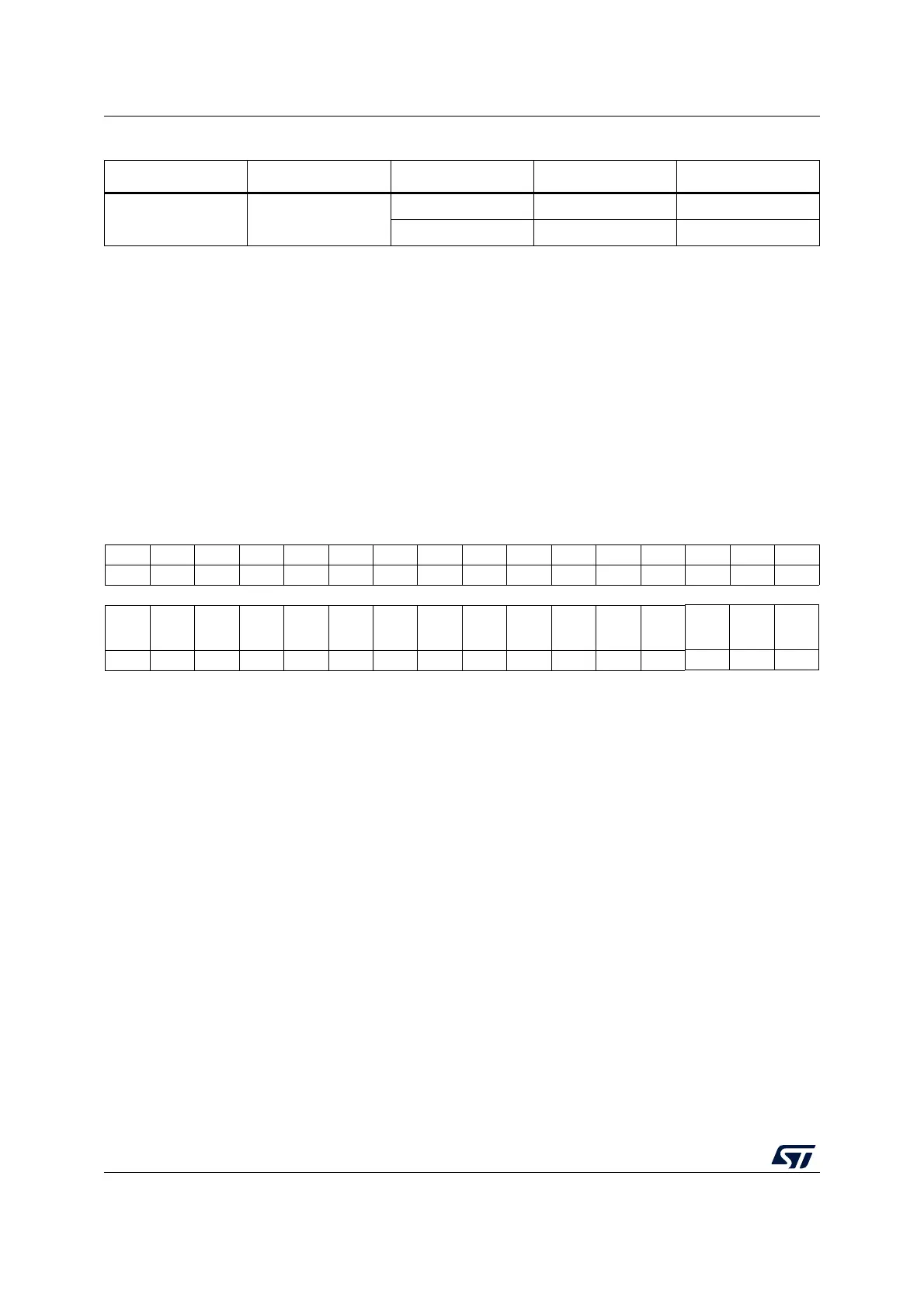

Table 254. DEV_ID and REV_ID field values

Device DEV_ID Revision code Revision number REV_ID

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DBG_

STAND

BY

DBG_

STOP

Res.

rw rw

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 DBG_STANDBY: Debug Standby and Shutdown modes

Debug options in Standby or Shutdown mode.

0: Digital part powered. From software point of view, exiting Standby and Shutdown modes

is identical as fetching reset vector (except for status bits indicating that the MCU exits

Standby)

1: Digital part powered and FCLK and HCLK running, derived from the internal RC oscillator

remaining active. The MCU generates a system reset so that exiting Standby and Shutdown

has the same effect as starting from reset.

Bit 1 DBG_STOP: Debug Stop mode

Debug options in Stop mode.

0: All clocks disabled, including FCLK and HCLK. Upon Stop mode exit, the CPU is clocked

by the HSI internal RC oscillator.

1: FCLK and HCLK running, derived from the internal RC oscillator remaining active. If

Systick is enabled, it may generate periodic interrupt and wake up events.

Upon Stop mode exit, the software must re-establish the desired clock configuration.

Loading...

Loading...