RM0444 Rev 5 161/1390

RM0444 Reset and clock control (RCC)

220

detection of internal reset sources by external components when the line faces a

significant capacitive load.

• Reset input

In this mode, any valid reset signal on the NRST pin is propagated to device internal

logic, but resets generated internally by the device are not visible on the pin. In this

configuration, GPIO functionality (PF2) is not available.

• GPIO

In this mode, the pin can be used as PF2 standard GPIO. The reset function of the pin

is not available. Reset is only possible from device internal reset sources and it is not

propagated to the pin.

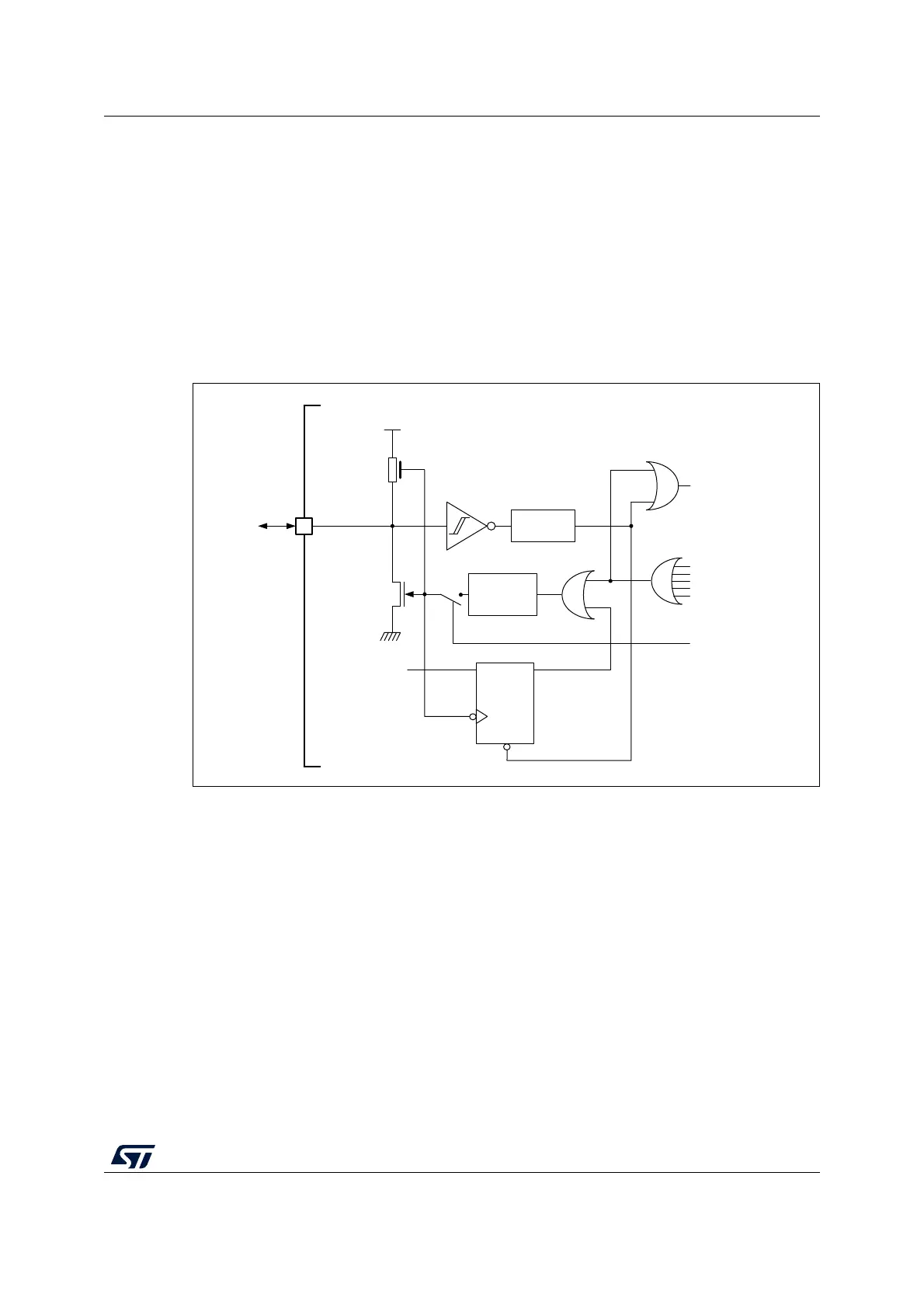

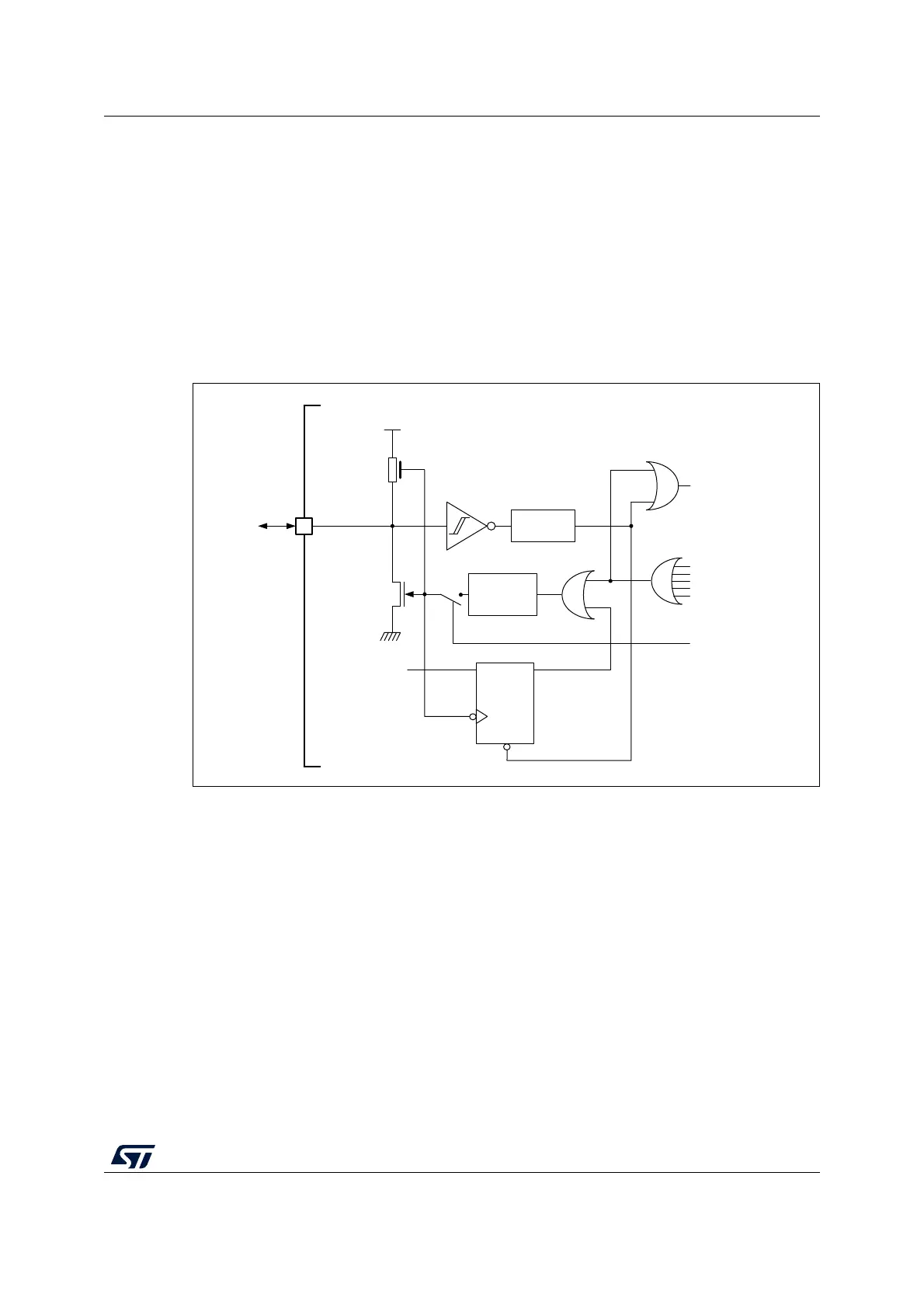

Figure 9. Simplified diagram of the reset circuit

Caution: Upon power reset or wakeup from shutdown mode, the NRST pin is configured as Reset

input/output and driven low by the system until it is reconfigured to the expected mode when

the option bytes are loaded, in the fourth clock cycle after the end of trstempo.

Software reset

The SYSRESETREQ bit in Cortex

®

-M0+ Application interrupt and reset control register

must be set to force a software reset on the device (refer to the programming manual

PM0223).

MSv47935V1

External

reset

V

DD

R

PU

Internal

reset sources

NRST

System reset

Filter

Pulse

generator

(min 20 μs)

D Q

CLEAR

Bidirectional

reset

Reset holder

Loading...

Loading...