Low-power timer (LPTIM) RM0444

840/1390 RM0444 Rev 5

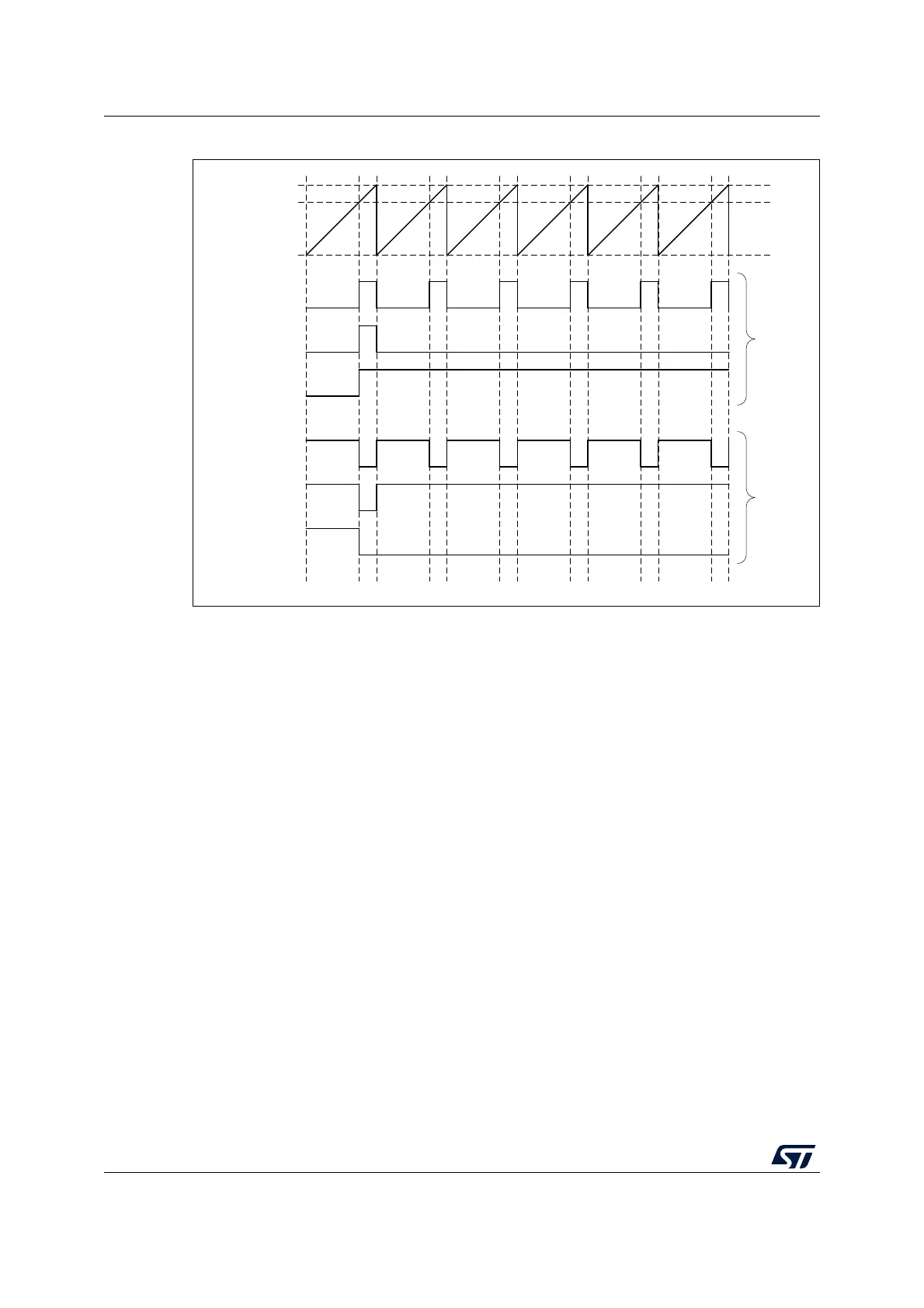

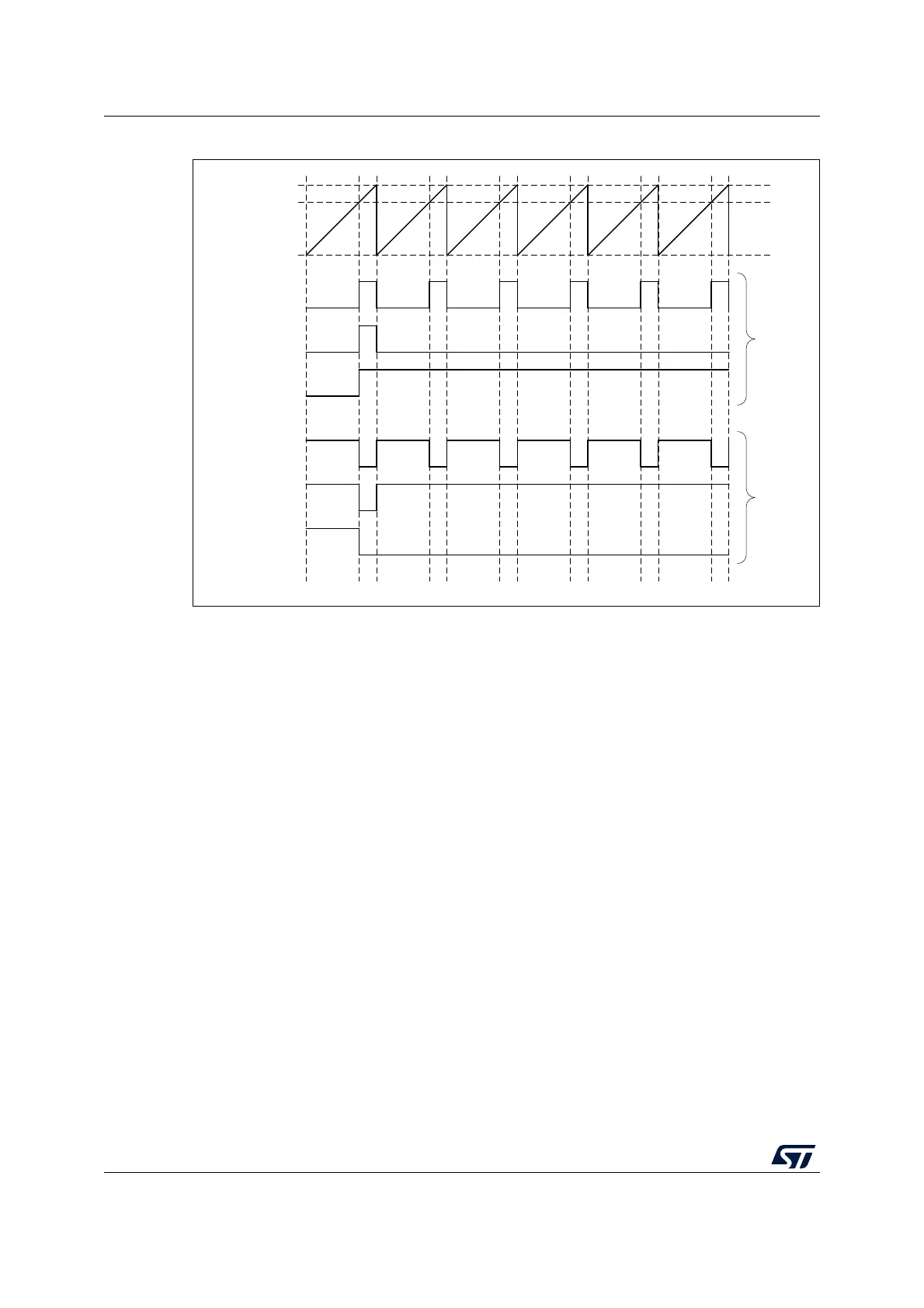

Figure 275. Waveform generation

26.4.11 Register update

The LPTIM_ARR register and LPTIM_CMP register are updated immediately after the APB

bus write operation, or at the end of the current period if the timer is already started.

The PRELOAD bit controls how the LPTIM_ARR and the LPTIM_CMP registers are

updated:

• When the PRELOAD bit is reset to ‘0’, the LPTIM_ARR and the LPTIM_CMP registers

are immediately updated after any write access.

• When the PRELOAD bit is set to ‘1’, the LPTIM_ARR and the LPTIM_CMP registers

are updated at the end of the current period, if the timer has been already started.

The LPTIM APB interface and the LPTIM kernel logic use different clocks, so there is some

latency between the APB write and the moment when these values are available to the

counter comparator. Within this latency period, any additional write into these registers must

be avoided.

The ARROK flag and the CMPOK flag in the LPTIM_ISR register indicate when the write

operation is completed to respectively the LPTIM_ARR register and the LPTIM_CMP

register.

After a write to the LPTIM_ARR register or the LPTIM_CMP register, a new write operation

to the same register can only be performed when the previous write operation is completed.

Any successive write before respectively the ARROK flag or the CMPOK flag be set, will

lead to unpredictable results.

MS32467V2

LPTIM_ARR

Compare

0

PWM

One shot

Set once

PWM

One shot

Set once

Pol = 0

Pol = 1

Loading...

Loading...