RM0444 Rev 5 429/1390

RM0444 Digital-to-analog converter (DAC)

441

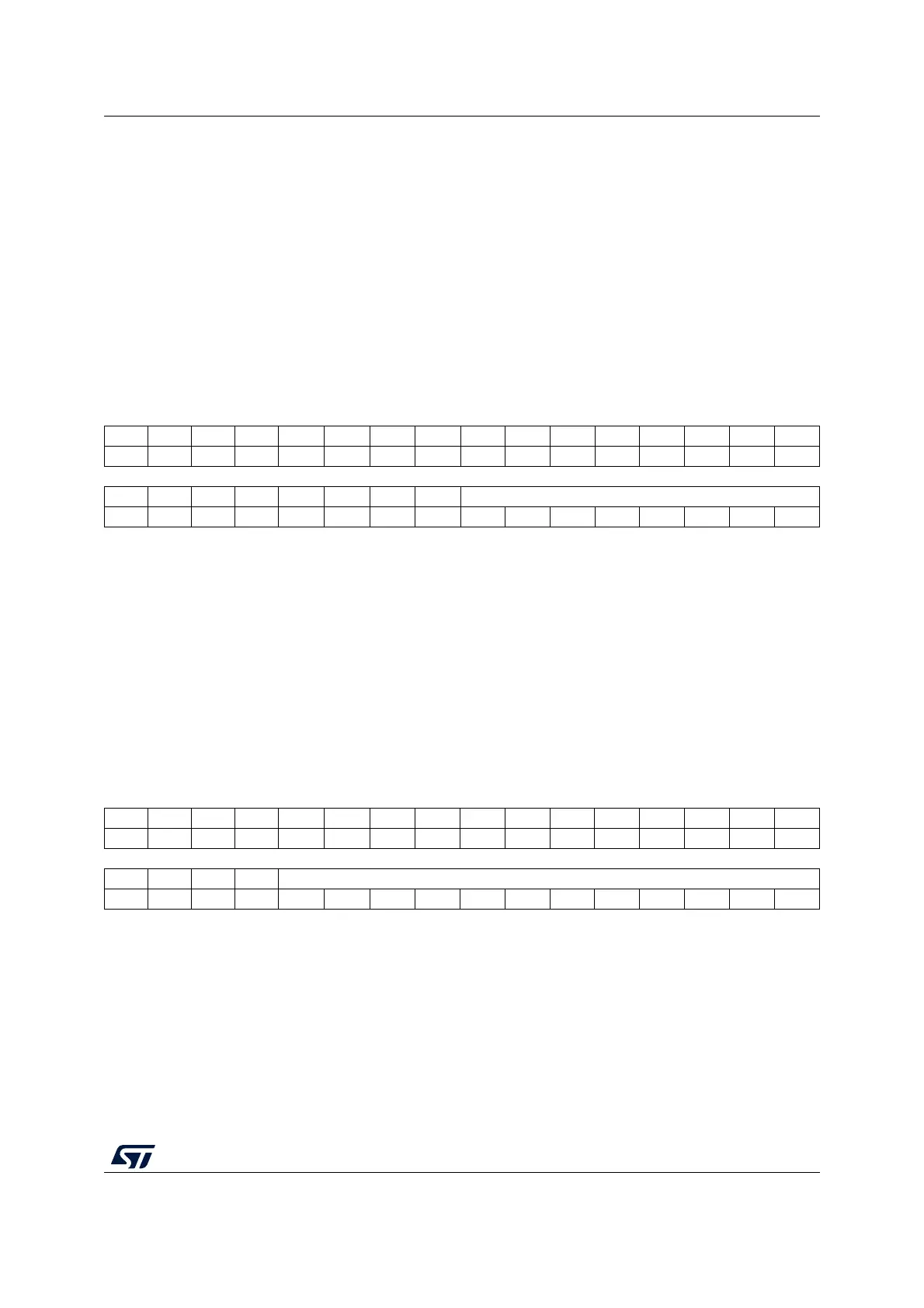

16.7.5 DAC channel1 8-bit right aligned data holding register

(DAC_DHR8R1)

Address offset: 0x10

Reset value: 0x0000 0000

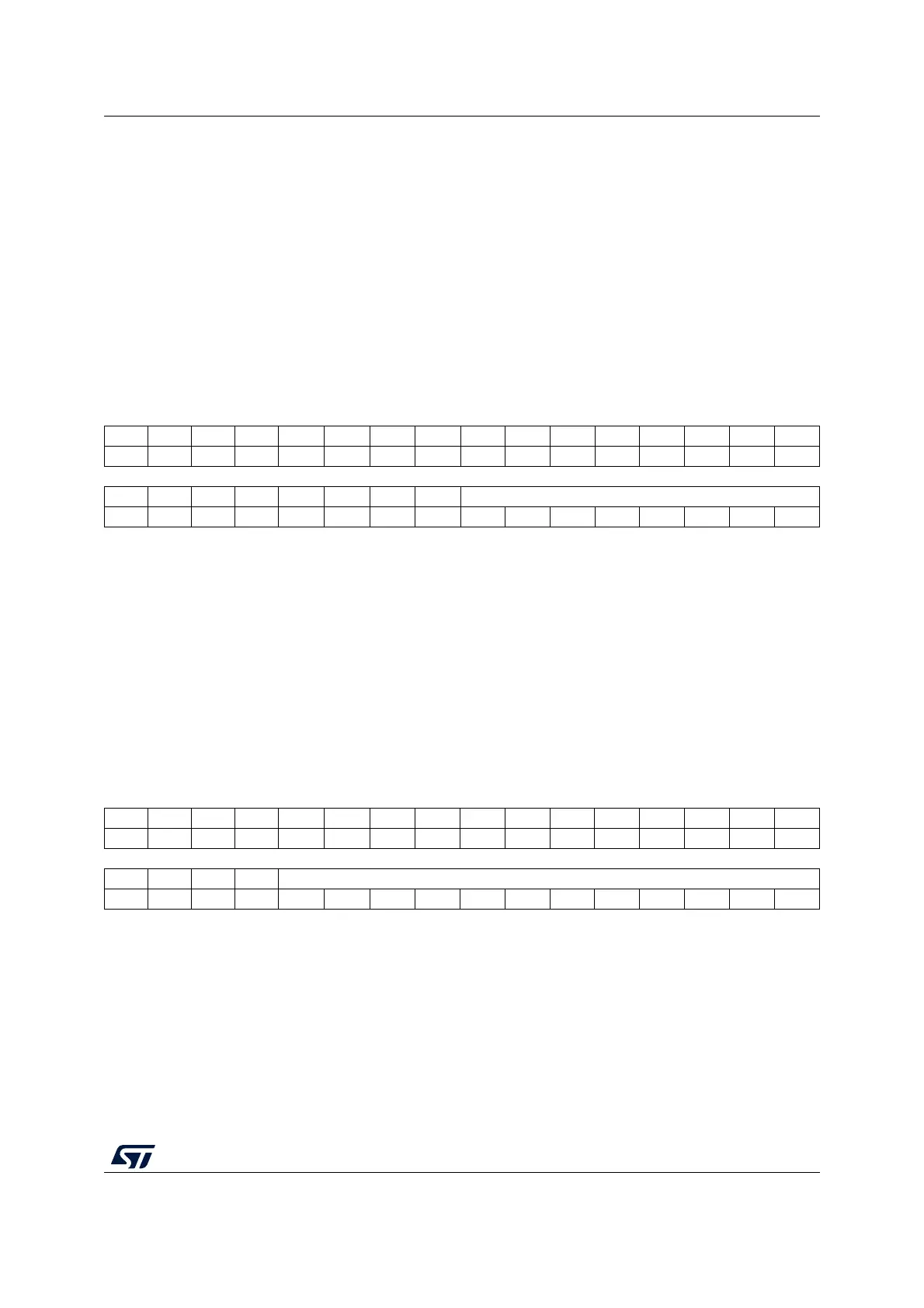

16.7.6 DAC channel2 12-bit right aligned data holding register

(DAC_DHR12R2)

This register is available only on dual-channel DACs. Refer to Section 16.3: DAC

implementation.

Address offset: 0x14

Reset value: 0x0000 0000

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:4 DACC1DHR[11:0]: DAC channel1 12-bit left-aligned data

These bits are written by software.

They specify 12-bit data for DAC channel1.

Bits 3:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. DACC1DHR[7:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 DACC1DHR[7:0]: DAC channel1 8-bit right-aligned data

These bits are written by software. They specify 8-bit data for DAC channel1.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. DACC2DHR[11:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:12 Reserved, must be kept at reset value.

Bits 11:0 DACC2DHR[11:0]: DAC channel2 12-bit right-aligned data

These bits are written by software. They specify 12-bit data for DAC channel2.

Loading...

Loading...