Universal serial bus full-speed host/device interface (USB) RM0444

1302/1390 RM0444 Rev 5

37.6.2 Buffer descriptor table

Note: The buffer descriptor table is located inside the packet buffer memory in the separate "USB

SRAM" address space.

Although the buffer descriptor table is located inside the packet buffer memory ("USB

SRAM" area), its entries can be considered as additional registers used to configure the

location and size of the packet buffers used to exchange data between the USB macro cell

and the device.

The first packet memory location is located at USB SRAM base address. The buffer

descriptor table entry associated with the USB_CHEPnR registers is described below. The

memory should be addressed using Word (32-bit) accesses.

A thorough explanation of packet buffers and the buffer descriptor table usage can be found

in Structure and usage of packet buffers on page 1268.

Channel/endpoint transmit buffer descriptor n (USB_CHEP_TXRXBD_n)

Address offset: n*8

This register description applies when corresponding CHEPnR register does not program

the use of double buffering (otherwise refer to following register description)

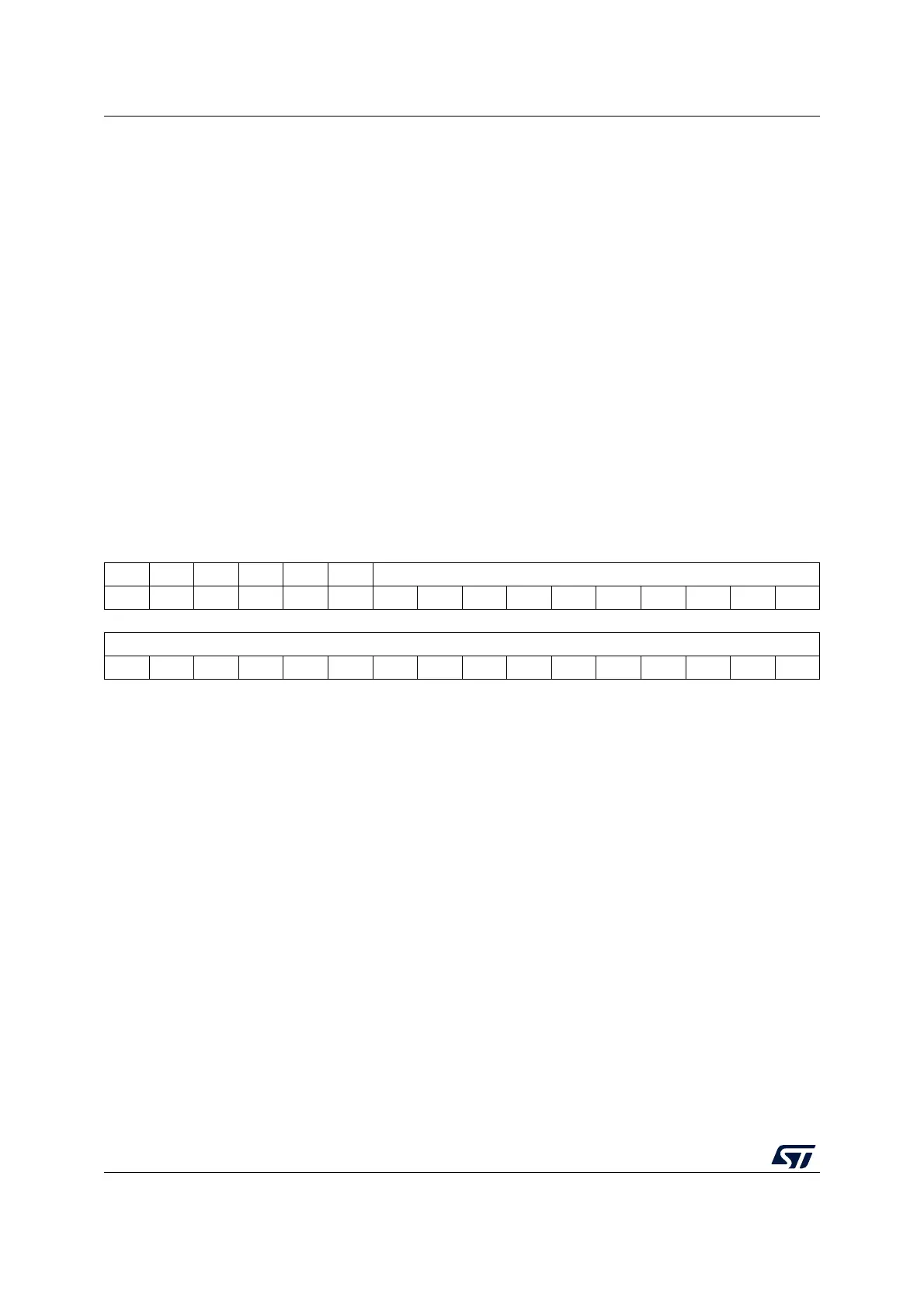

Channel/endpoint receive buffer descriptor n [alternate]

(USB_CHEP_TXRXBD_n)

Address offset: n*8

This register description applies when corresponding CHEPnR register programs the use of

double buffering and activates receive buffers (otherwise refer to previous register

description).

This table location is used to store two different values, both required during packet

reception. The most significant bits contains the definition of allocated buffer size, to allow

buffer overflow detection, while the least significant part of this location is written back by the

USB peripheral at the end of reception to give the actual number of received bytes. Due to

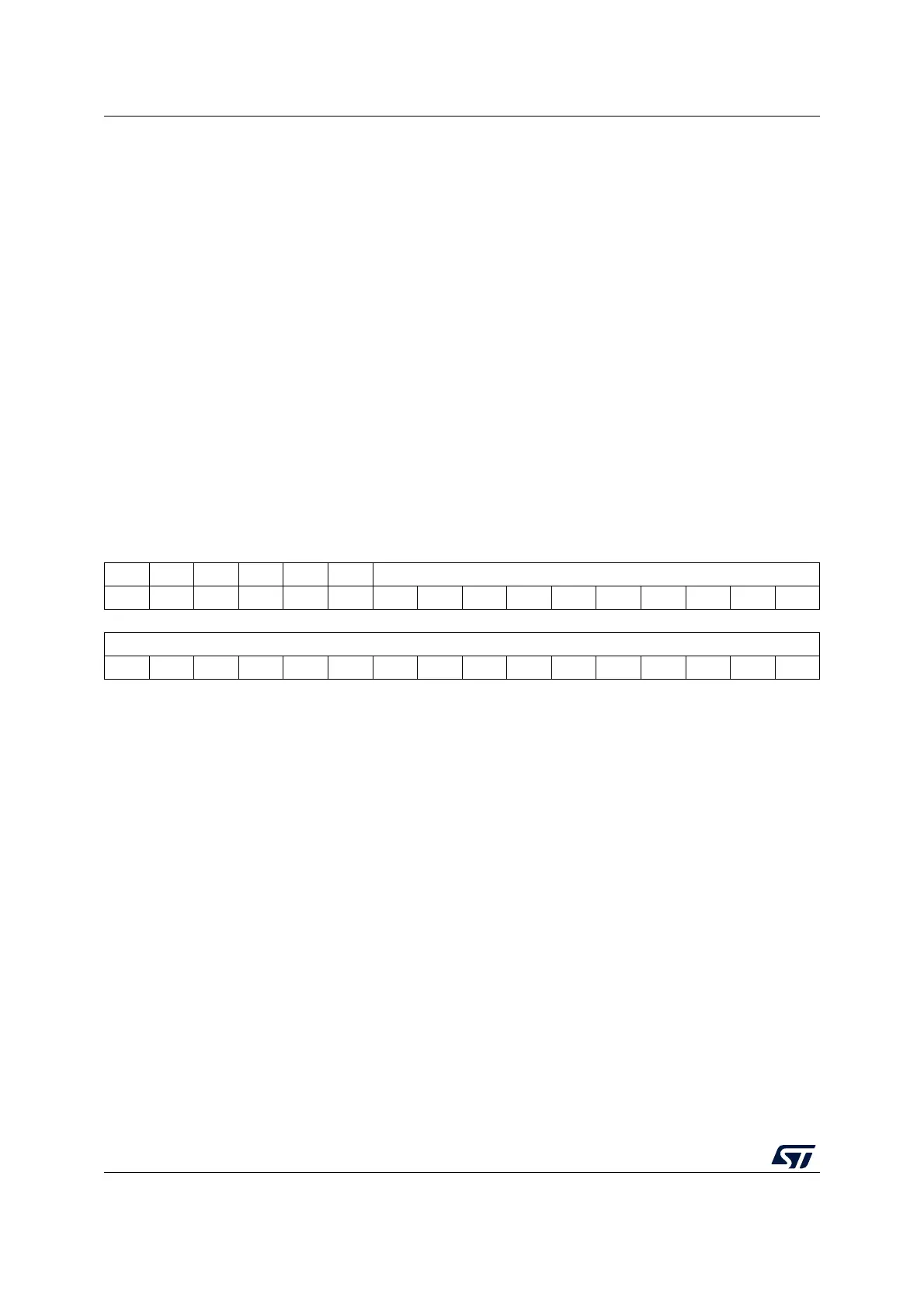

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. COUNTn_TX[9:0]

rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

ADDRn_TX[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:26 Reserved, must be kept at reset value.

Bits 25:16 COUNTn_TX[9:0]: Transmission byte count

These bits contain the number of bytes to be transmitted by the endpoint/channel associated

with the USB_CHEPnR register at the next IN token addressed to it.

Bits 15:0 ADDRn_TX[15:0]: Transmission buffer address

These bits point to the starting address of the packet buffer containing data to be transmitted

by the endpoint/channel associated with the USB_CHEPnR register at the next IN token

addressed to it. Bits 1 and 0 must always be written as “00” since packet memory is word

wide and all packet buffers must be word aligned.

Loading...

Loading...