RM0444 Rev 5 1175/1390

RM0444 Serial peripheral interface / integrated interchip sound (SPI/I2S)

1195

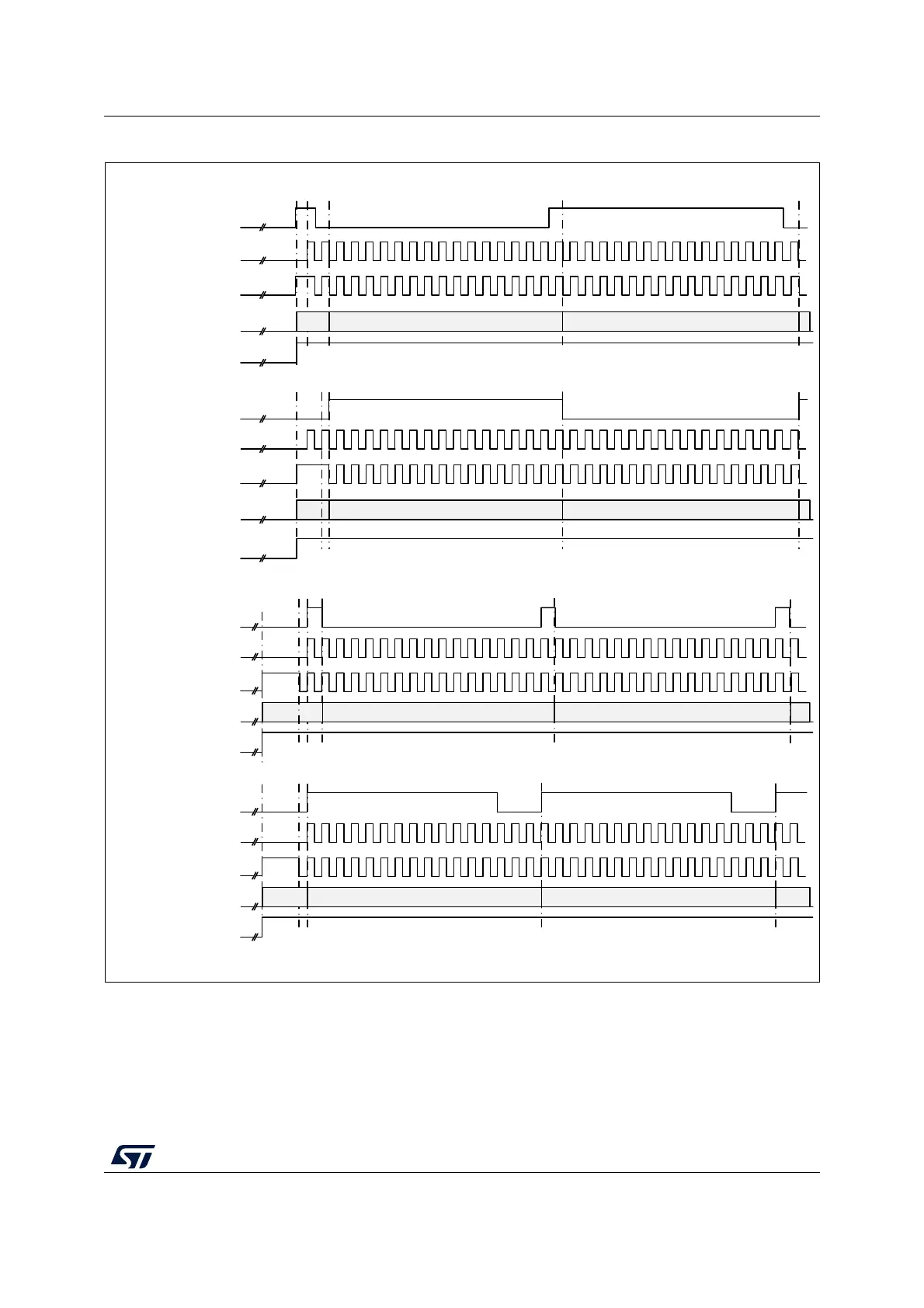

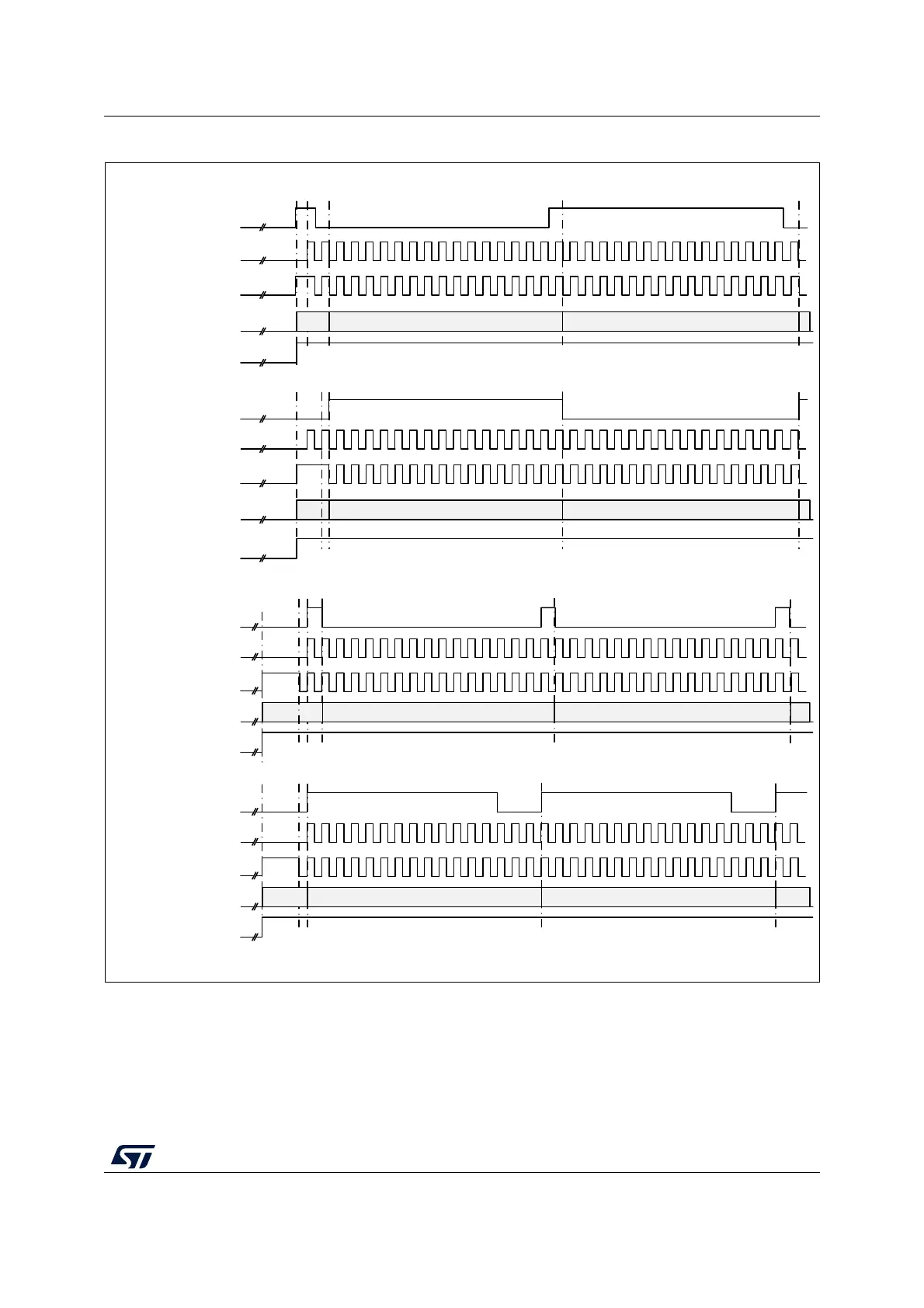

Figure 389. Start sequence in master mode

In slave mode, the way the frame synchronization is detected, depends on the value of

ASTRTEN bit.

If ASTRTEN = 0, when the audio interface is enabled (I2SE = 1), then the hardware waits for

the appropriate transition on the incoming WS signal, using the CK signal.

MSv37520V2

dum: not significant data

WS (O)

SD (O)

CK (O),

CKPOL = 0

Left sample Right sample

I2SE

WS (O)

CK (O),

CKPOL = 1

SD (O)

Left sample Right sample

WS (O)

SD (O)

Sample1 Sample 2

Master I2S Philips Standard

Master I2S MSB or LSB justified

Master PCM short frame

I2SE

I2SE

CK (O),

CKPOL = 0

CK (O),

CKPOL = 1

CK (O),

CKPOL = 0

CK (O),

CKPOL = 1

dum

dum

dum

I2SE

WS (O)

SD (O)

Sample1 Sample 2

Master PCM long frame

CK (O),

CKPOL = 0

CK (O),

CKPOL = 1

dum

Loading...

Loading...