Power control (PWR) RM0444

146/1390 RM0444 Rev 5

4.4.3 Power control register 3 (PWR_CR3)

Address offset: 0x08

Reset value: 0x0000 8000. This register is not reset when exiting Standby modes and with

the PWRRST bit in the APB peripheral reset register 1 (RCC_APBRSTR1).

Access: Additional APB cycles are needed to access this register vs. a standard APB

access (3 for a write and 2 for a read).

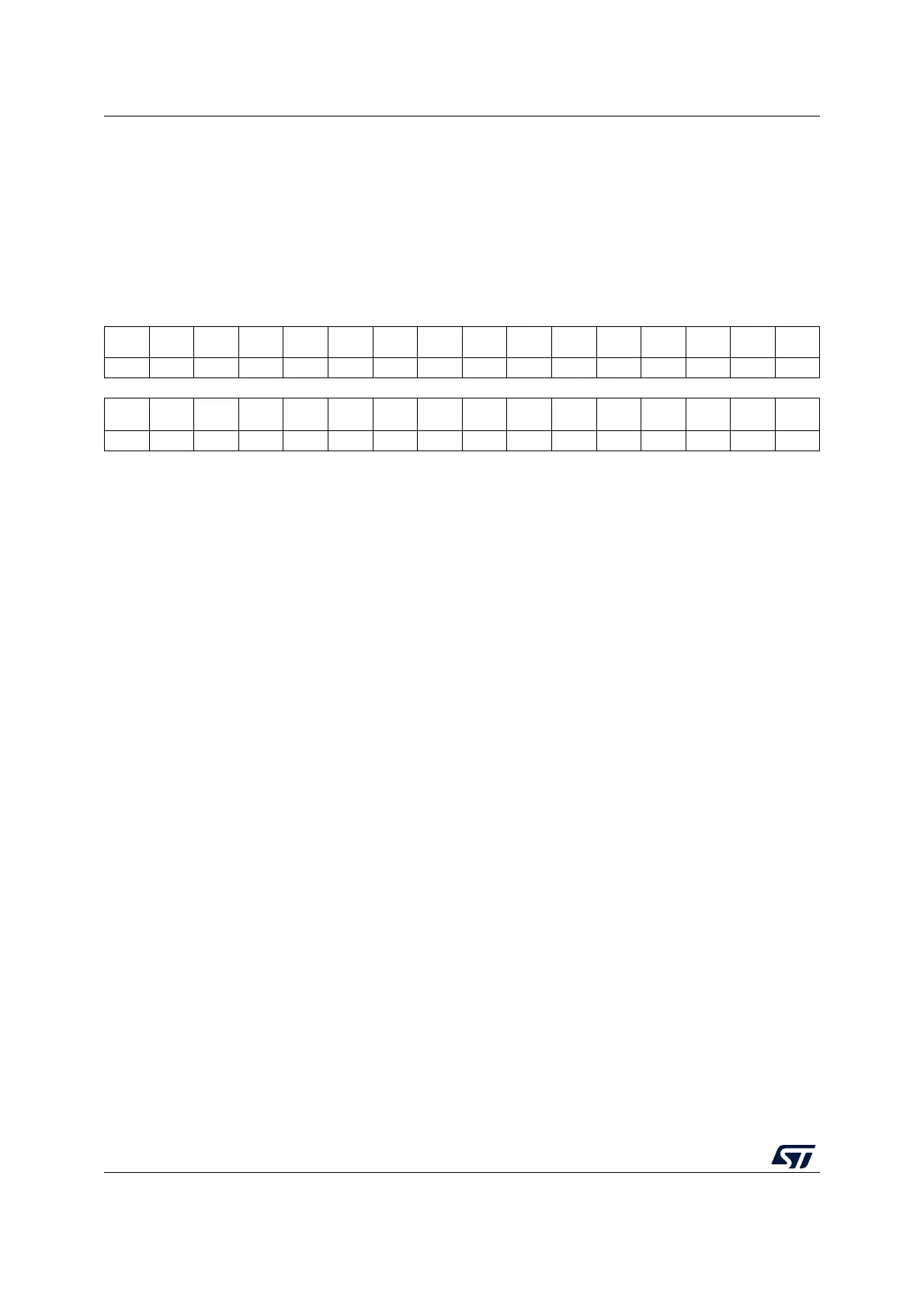

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

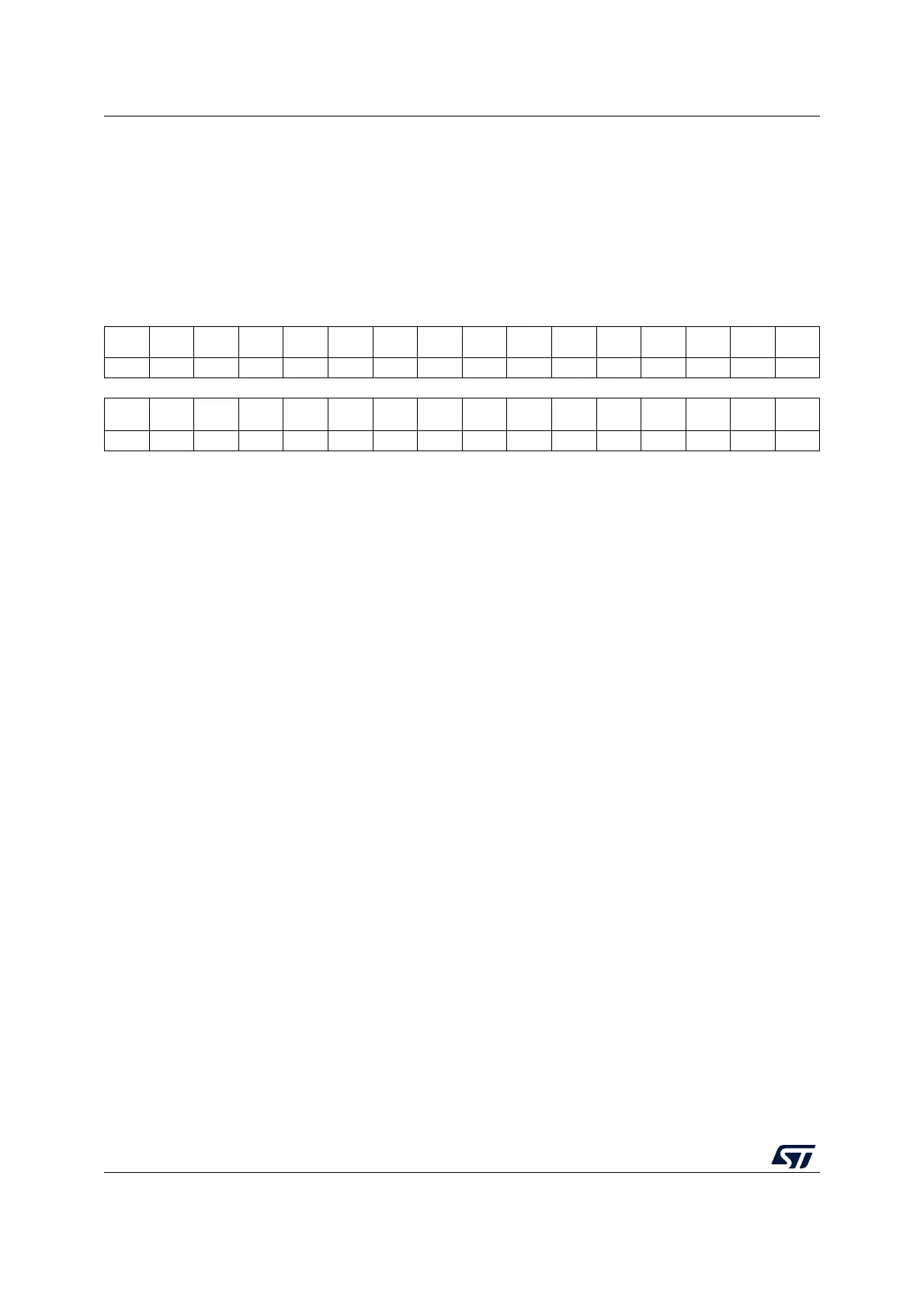

1514131211109876543210

EIWUL Res. Res. Res. Res. APC

ENB_

ULP

RRS Res. Res.

EWUP

6

EWUP

5

EWUP

4

EWUP

3

EWUP

2

EWUP

1

rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 EIWUL: Enable internal wakeup line

0: Disable

1: Enable

Bits 14:11 Reserved, must be kept at reset value.

Bit 10 APC: Apply pull-up and pull-down configuration

This bit determines whether the I/O pull-up and pull-down configurations defined in the

PWR_PUCRx and PWR_PDCRx registers are applied.

0: Not applied

1: Applied

Bit 9 ENB_ULP: Ultra-low-power enable

Enable/disable periodical sampling of supply voltage in Stop and Standby modes for

detecting condition of PDR and BOR reset.

0: Disable (the supply voltage is monitored continuously)

1: Enable

When set, the supply voltage is sampled for PDR/BOR reset condition only periodically and

not continuously, in order to save power.

Caution: When enabled, and if the supply voltage drops below the minimum

operating condition between two supply voltage samples, the reset

condition is missed and no reset is generated.

Bit 8 RRS: SRAM retention in Standby mode

The bit determines whether the SRAM is powered (from low-power regulator) and retains its

contents, or unpowered and loses its contents.

0: Unpowered - contents lost

1: Powered - contents retained

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 EWUP6: Enable WKUP6 wakeup pin

When this bit is set, the WKUP6 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs. The active edge is

configured through WP6 bit in the PWR_CR4 register.

Loading...

Loading...