General-purpose timers (TIM15/TIM16/TIM17) RM0444

758/1390 RM0444 Rev 5

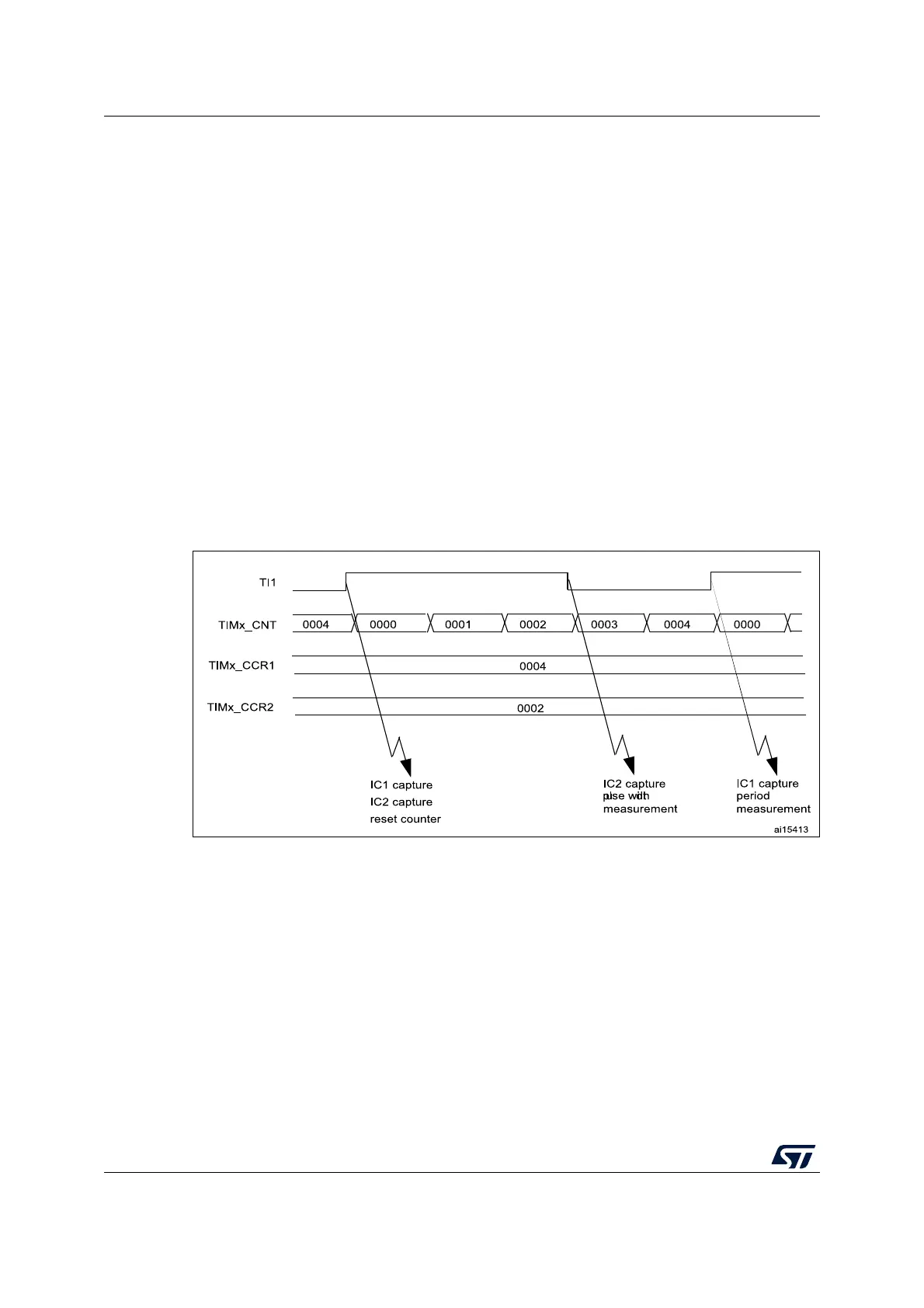

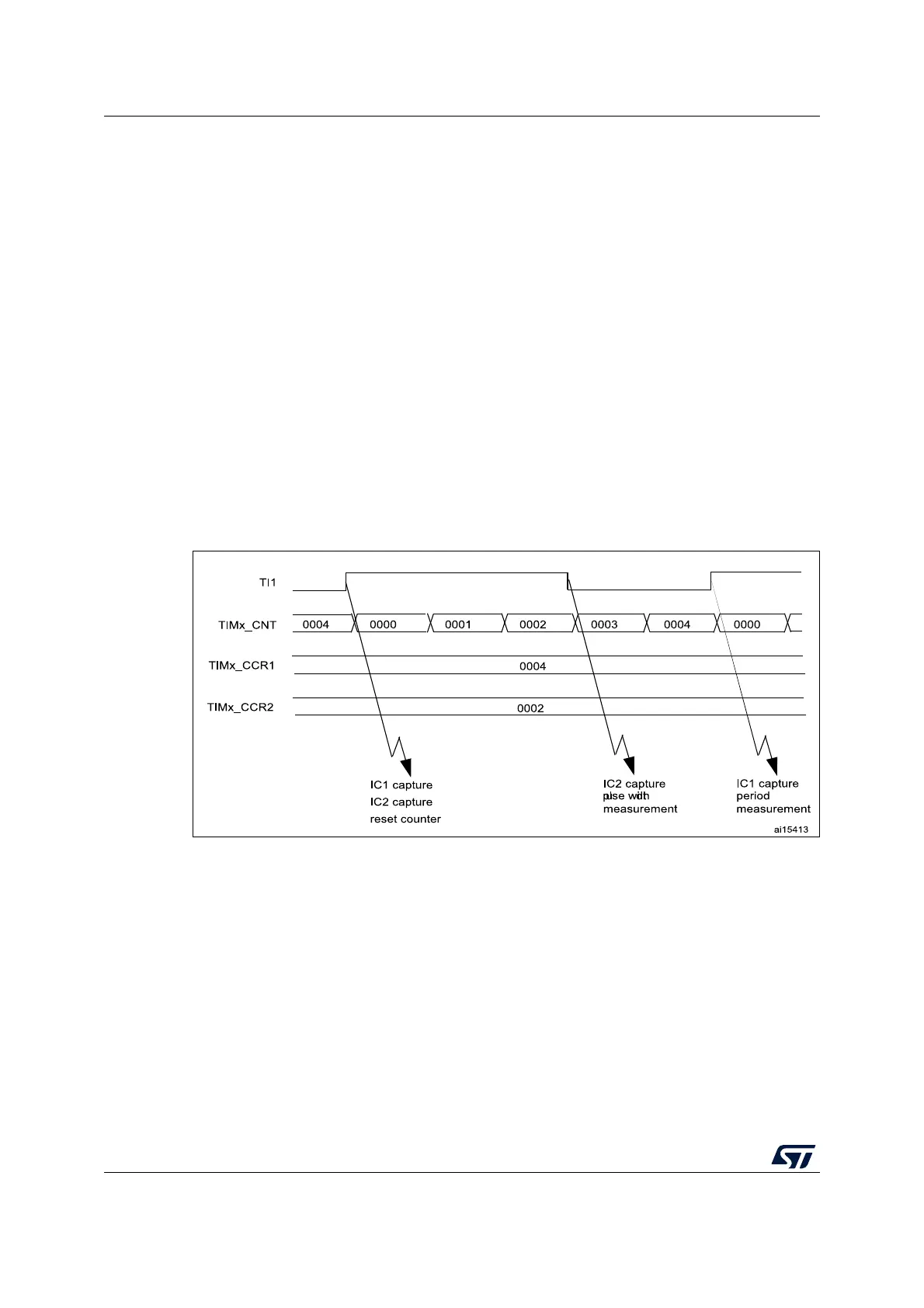

For example, one can measure the period (in TIMx_CCR1 register) and the duty cycle (in

TIMx_CCR2 register) of the PWM applied on TI1 using the following procedure (depending

on CK_INT frequency and prescaler value):

1. Select the proper TI1[x] source (internal or external) with the TI1SEL[3:0] bits in the

TIMx_TISEL register.

2. Select the active input for TIMx_CCR1: write the CC1S bits to 01 in the TIMx_CCMR1

register (TI1 selected).

3. Select the active polarity for TI1FP1 (used both for capture in TIMx_CCR1 and counter

clear): write the CC1P and CC1NP bits to ‘0’ (active on rising edge).

4. Select the active input for TIMx_CCR2: write the CC2S bits to 10 in the TIMx_CCMR1

register (TI1 selected).

5. Select the active polarity for TI1FP2 (used for capture in TIMx_CCR2): write the CC2P

and CC2NP bits to ‘10’ (active on falling edge).

6. Select the valid trigger input: write the TS bits to 00101 in the TIMx_SMCR register

(TI1FP1 selected).

7. Configure the slave mode controller in reset mode: write the SMS bits to 100 in the

TIMx_SMCR register.

8. Enable the captures: write the CC1E and CC2E bits to ‘1’ in the TIMx_CCER register.

Figure 254. PWM input mode timing

1. The PWM input mode can be used only with the TIMx_CH1/TIMx_CH2 signals due to the fact that only

TI1FP1 and TI2FP2 are connected to the slave mode controller.

25.4.8 Forced output mode

In output mode (CCxS bits = 00 in the TIMx_CCMRx register), each output compare signal

(OCxREF and then OCx/OCxN) can be forced to active or inactive level directly by software,

independently of any comparison between the output compare register and the counter.

To force an output compare signal (OCXREF/OCx) to its active level, one just needs to write

101 in the OCxM bits in the corresponding TIMx_CCMRx register. Thus OCXREF is forced

high (OCxREF is always active high) and OCx get opposite value to CCxP polarity bit.

For example: CCxP=0 (OCx active high) => OCx is forced to high level.

The OCxREF signal can be forced low by writing the OCxM bits to 100 in the TIMx_CCMRx

register.

Loading...

Loading...