Universal synchonous receiver transmitter (USART) RM0444

1044/1390 RM0444 Rev 5

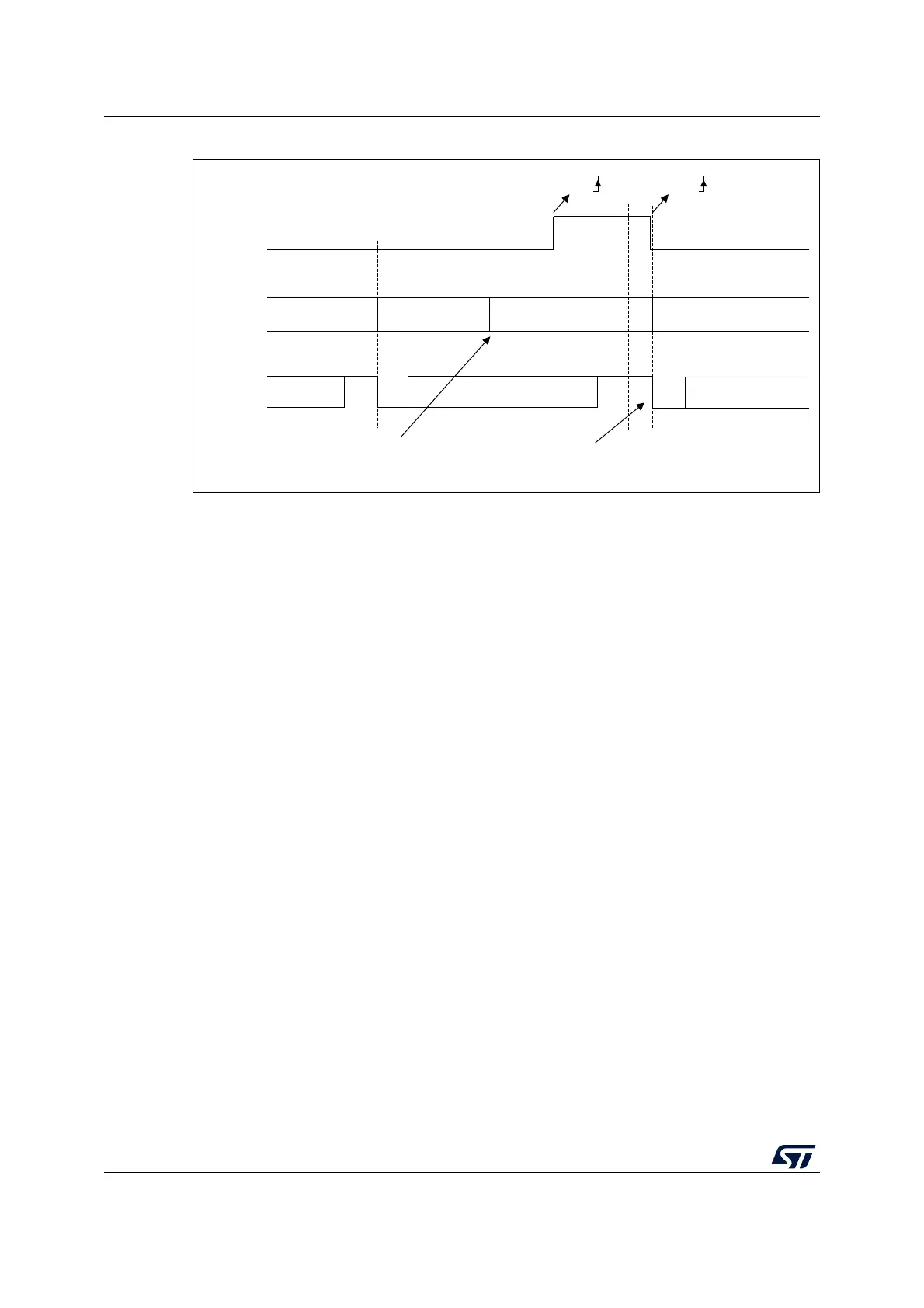

Figure 338. RS232 CTS flow control

Note: For correct behavior, nCTS must be asserted at least 3 USART clock source periods before

the end of the current character. In addition it should be noted that the CTSCF flag may not

be set for pulses shorter than 2 x PCLK periods.

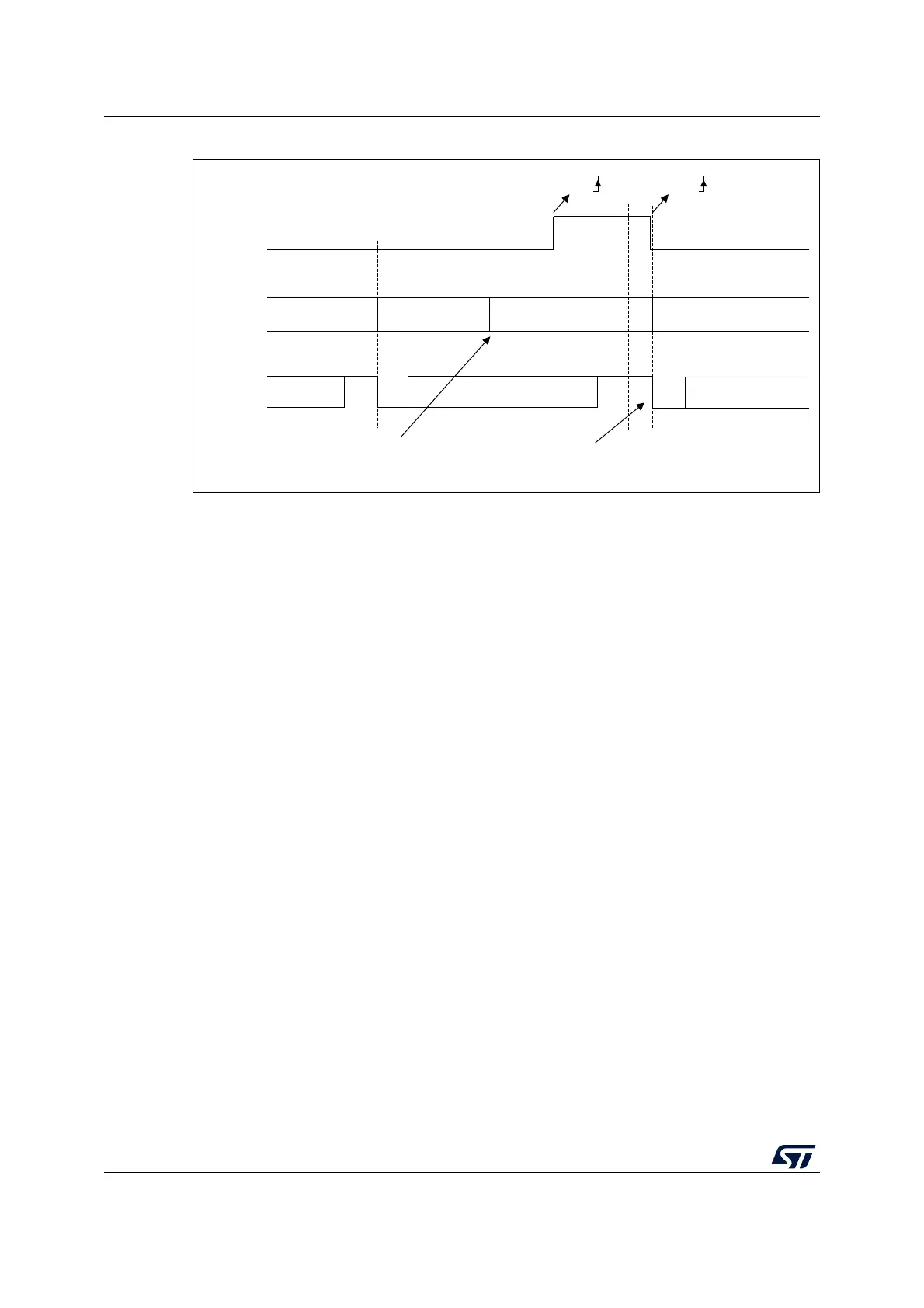

RS485 driver enable

The driver enable feature is enabled by setting bit DEM in the USART_CR3 control register.

This enables the user to activate the external transceiver control, through the DE (Driver

Enable) signal. The assertion time is the time between the activation of the DE signal and

the beginning of the start bit. It is programmed using the DEAT [4:0] bitfields in the

USART_CR1 control register. The deassertion time is the time between the end of the last

stop bit, in a transmitted message, and the de-activation of the DE signal. It is programmed

using the DEDT [4:0] bitfields in the USART_CR1 control register. The polarity of the DE

signal can be configured using the DEP bit in the USART_CR3 control register.

In USART, the DEAT and DEDT are expressed in sample time units (1/8 or 1/16 bit time,

depending on the oversampling rate).

MSv31167V1

Start

bit

Stop

bit

TX

TDR

CTS

Data 1

Data 2

Stop

bit

Idle

Start

bit

Data 2 Data 3

Data 3

empty empty

CTS

nCTS

Transmit data register

Writing data 3 in TDR

Transmission of Data 3 is

delayed until nCTS = 0

Loading...

Loading...