RM0444 Rev 5 151/1390

RM0444 Power control (PWR)

159

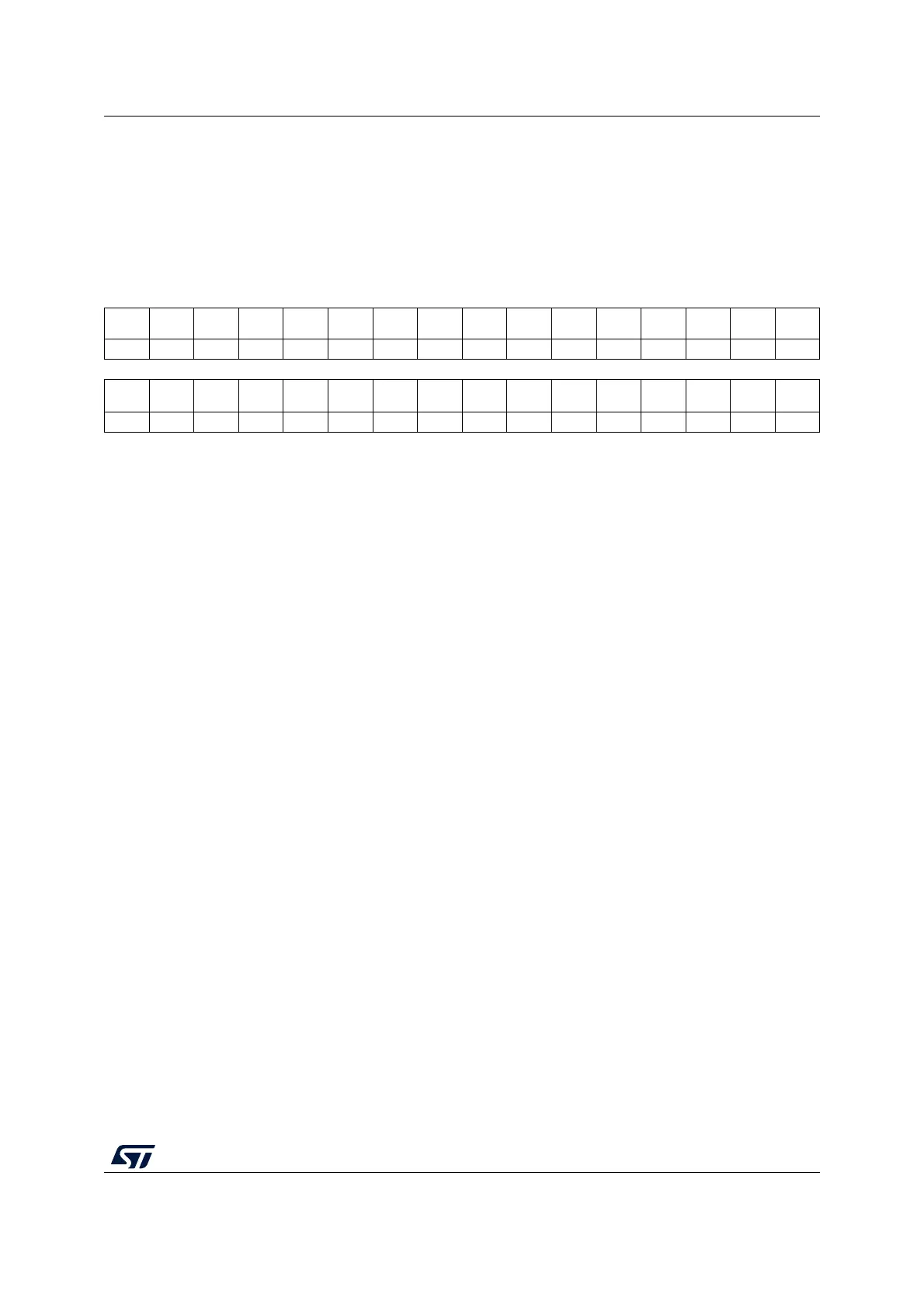

4.4.7 Power status clear register (PWR_SCR)

Address offset: 0x18

Reset value: 0x0000 0000.

Access: three additional APB cycles are needed to write this register, compared to a

standard APB write.

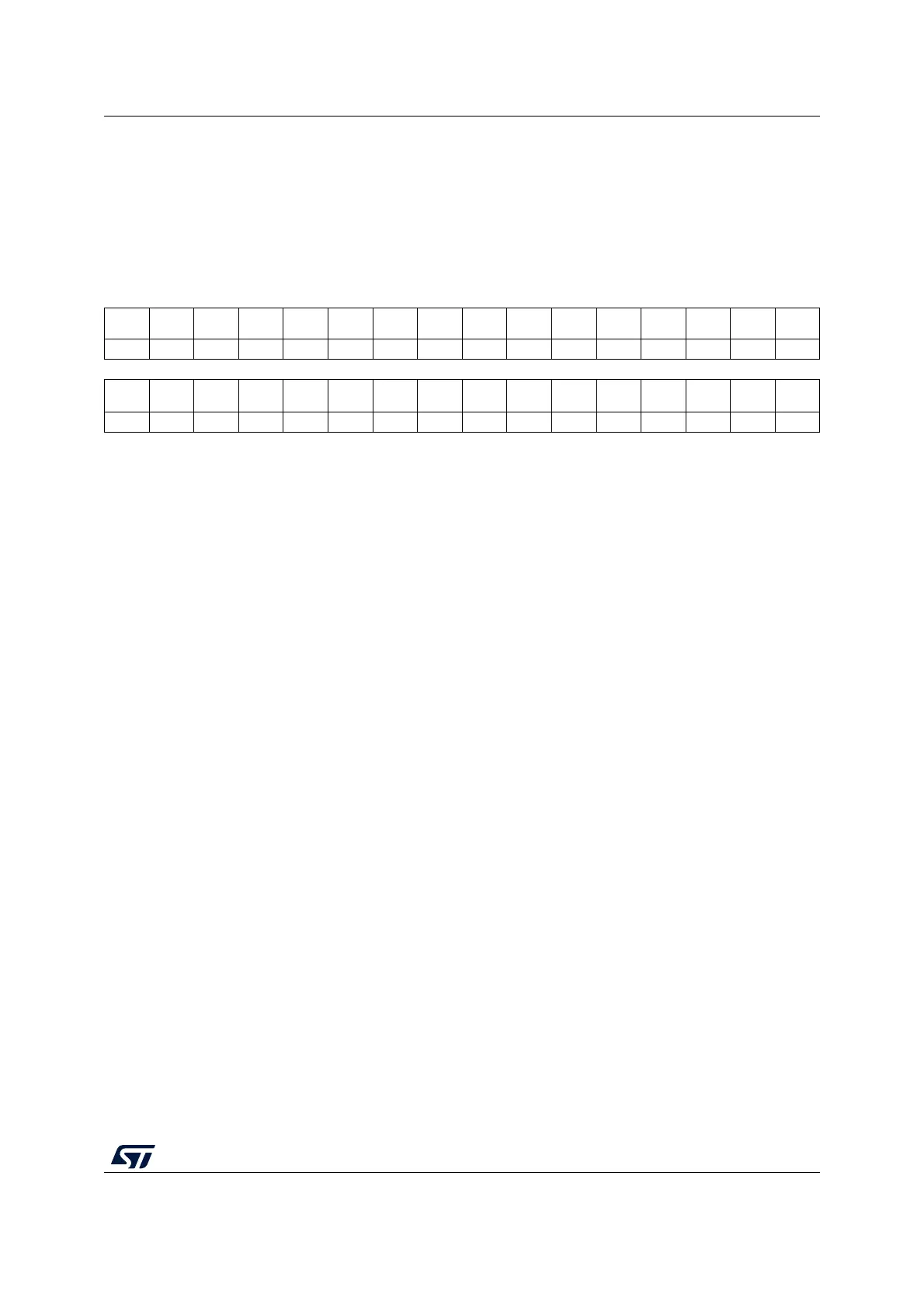

4.4.8 Power Port A pull-up control register (PWR_PUCRA)

Address offset: 0x20

Reset value: 0x0000 0000. This register is not reset when exiting Standby modes and with

PWRRST bit in the APB peripheral reset register 1 (RCC_APBRSTR1).

Access: Additional APB cycles are needed to access this register vs. a standard APB

access (3 for a write and 2 for a read).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. CSBF Res. Res.

CWUF

6

CWUF

5

CWUF

4

CWUF

3

CWUF

2

CWUF

1

w wwwwww

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 CSBF: Clear standby flag

Setting this bit clears the SBF flag in the PWR_SR1 register.

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 CWUF6: Clear wakeup flag 6

Setting this bit clears the WUF6 flag in the PWR_SR1 register.

Bit 4 CWUF5: Clear wakeup flag 5

Setting this bit clears the WUF5 flag in the PWR_SR1 register.

Bit 3 CWUF4: Clear wakeup flag 4

Setting this bit clears the WUF4 flag in the PWR_SR1 register.

Bit 2 CWUF3: Clear wakeup flag 3

Setting this bit clears the WUF3 flag in the PWR_SR1 register.

Bit 1 CWUF2: Clear wakeup flag 2

Setting this bit clears the WUF2 flag in the PWR_SR1 register.

Bit 0 CWUF1: Clear wakeup flag 1

Setting this bit clears the WUF1 flag in the PWR_SR1 register.

Loading...

Loading...