RM0444 Rev 5 323/1390

RM0444 Extended interrupt and event controller (EXTI)

335

13.4 EXTI functional behavior

The direct event inputs are enabled in the respective peripheral generating the wakeup

event. The configurable events are enabled by enabling at least one of the trigger edges.

Once an event input is enabled, the generation of a CPU wakeup is conditioned by the CPU

interrupt mask and CPU event mask.

For configurable event inputs, upon an edge on the event input, an event request is

generated if that edge (rising or/and falling) is enabled. When the associated CPU interrupt

is unmasked, the corresponding RPIFn and/or FPIFn bit is/are set in the EXTI_RPR or/and

EXTI_FPR register, waking up the CPU subsystem and activating CPU interrupt signal. The

RPIFn and/or FPIFn pending bit is cleared by writing 1 to it, which clears the CPU interrupt

request.

For direct event inputs, when enabled in the associated peripheral, an event request is

generated on the rising edge only. There is no corresponding CPU pending bit in the EXTI.

When the associated CPU interrupt is unmasked, the corresponding CPU subsystem is

woken up. The CPU is woken up (interrupted) by the peripheral synchronous interrupt.

The CPU event must be unmasked to generate an event. Upon an enabled edge occurring

on an event input, a CPU event pulse is generated. There is no event pending bit.

For the configurable event inputs, the software can generate an event request by setting the

corresponding bit of the software interrupt/event register EXTI_SWIER1, which has the

effect of a rising edge on the event input. The pending rising edge event flag is set in the

EXTI_RPR1 register, irrespective of the EXTI_RTSR1 register setting.

34 V

DDIO2

monitoring configurable Direct

35 LPUART2 wakeup Direct

Table 62. EXTI line connections (continued)

EXTI line Line source Line type

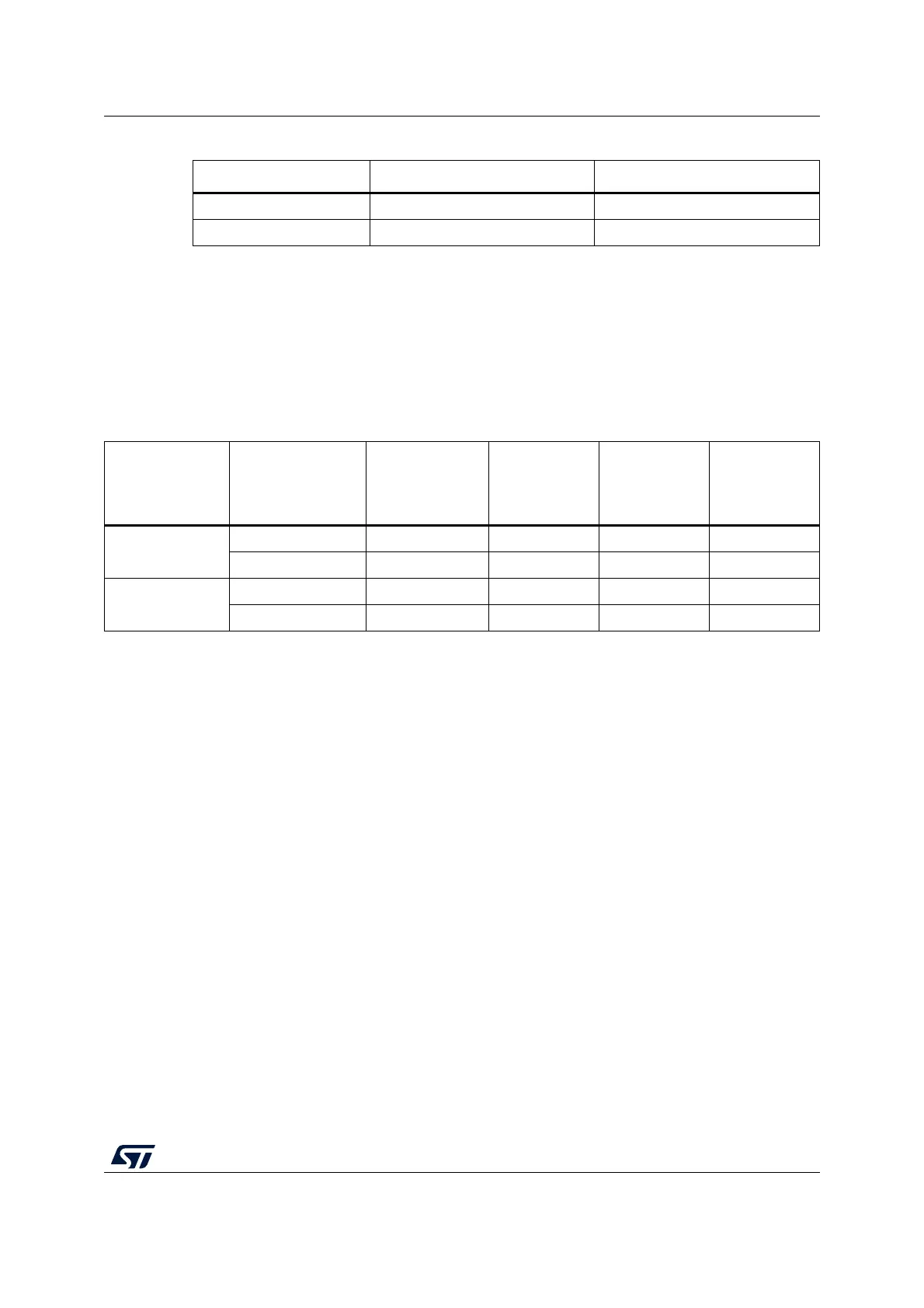

Table 63. Masking functionality

CPU interrupt

enable

EXTI_IMR.IMn

CPU event enable

EXTI_EMR.EMn

Configurable

event inputs

EXTI_RPR.RPIFn

EXTI_FPR.FPIFn

exti(n)

interrupt

(1)

CPU

event

CPU wakeup

0

0 No Masked Masked Masked

1 No Masked Yes Yes

1

0 Status latched Yes Masked Yes

(2)

1 Status latched Yes Yes Yes

1. The single exti(n) interrupt goes to the CPU. If no interrupt is required for CPU, the exti(n) interrupt must be masked in the

CPU NVIC.

2. Only if CPU interrupt is enabled in EXTI_IMR.IMn.

Loading...

Loading...