USB Type-C™ / USB Power Delivery interface (UCPD) RM0444

1344/1390 RM0444 Rev 5

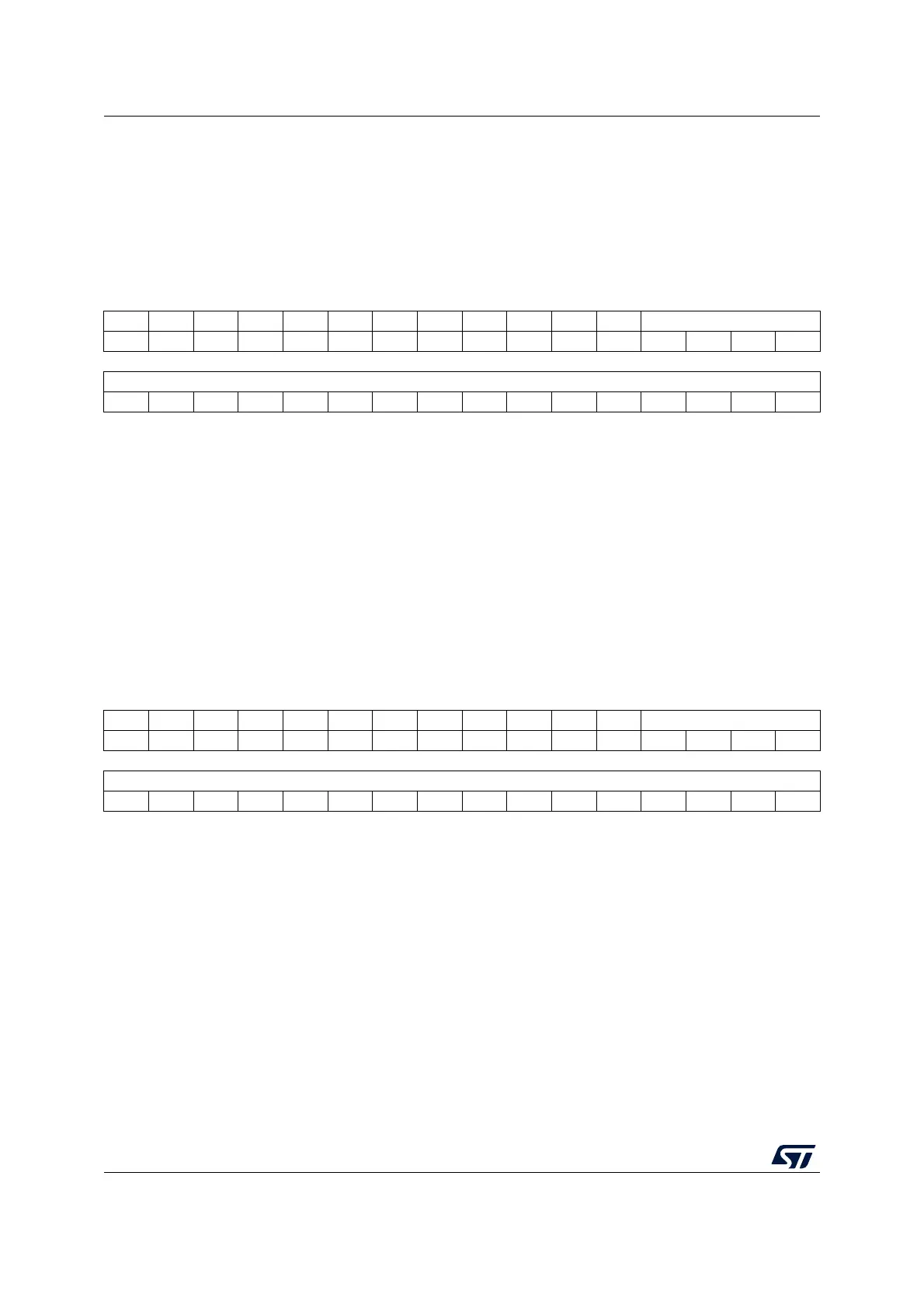

38.7.14 UCPD Rx ordered set extension register 1

(UCPD_RX_ORDEXTR1)

Address offset: 0x034

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is disabled (UCPDEN = 0).

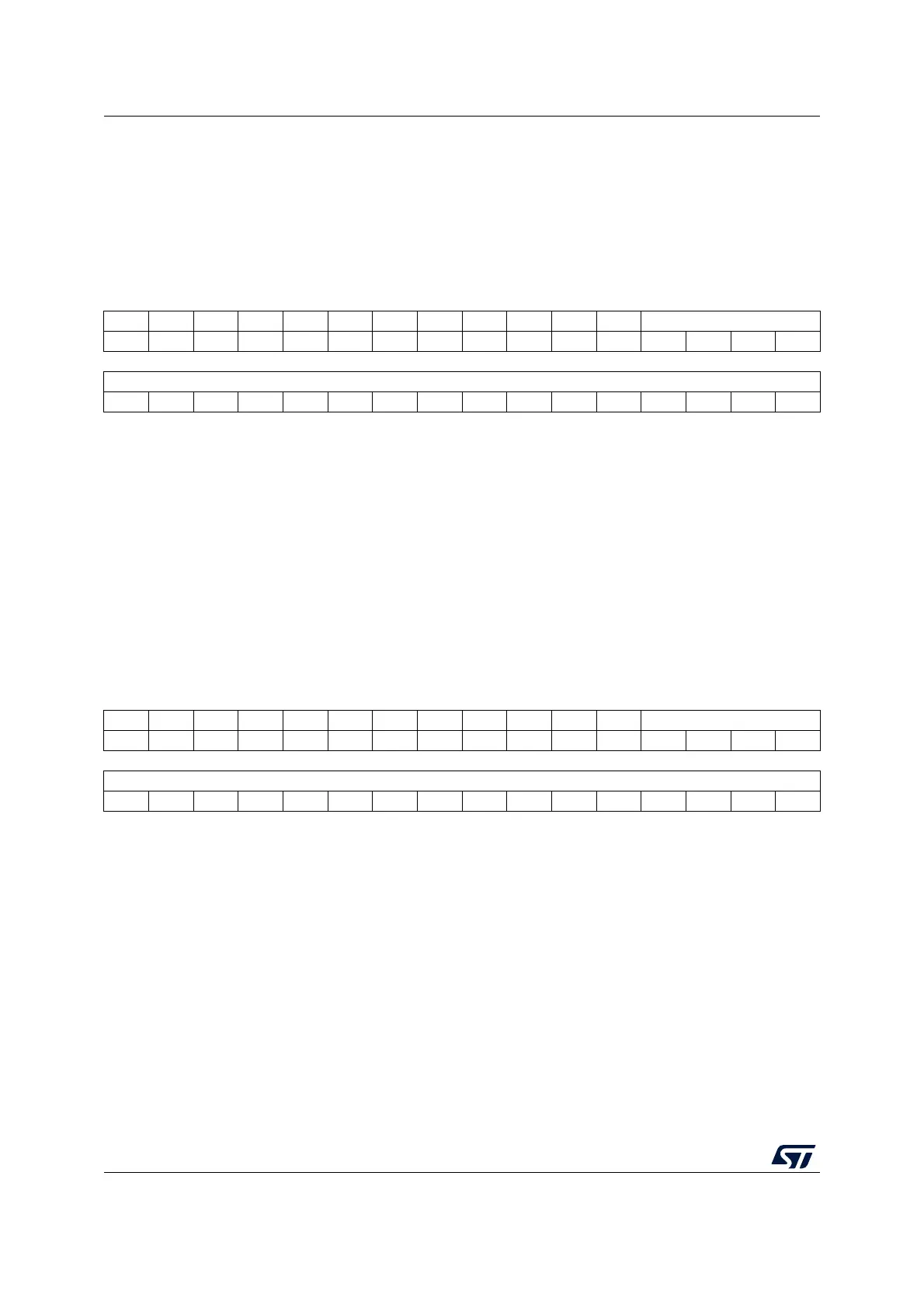

38.7.15 UCPD Rx ordered set extension register 2

(UCPD_RX_ORDEXTR2)

Address offset: 0x038

Reset value: 0x0000 0000

Writing to this register is only effective when the peripheral is disabled (UCPDEN = 0).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RXSOPX1[19:16]

rw rw rw rw

1514131211109876543210

RXSOPX1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:0 RXSOPX1[19:0]: Ordered set 1 received

The bitfield contains a full 20-bit sequence received, consisting of four K-codes, each of five

bits. The bit 0 (bit 0 of K-code1) is receive first, the bit 19 (bit 4 of K-code4) last.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. RXSOPX2[19:16]

rw rw rw rw

1514131211109876543210

RXSOPX2[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:0 RXSOPX2[19:0]: Ordered set 2 received

The bitfield contains a full 20-bit sequence received, consisting of four K-codes, each of five

bits. The bit 0 (bit 0 of K-code1) is receive first, the bit 19 (bit 4 of K-code4) last.

Loading...

Loading...