RM0444 Rev 5 1373/1390

RM0444 Debug support (DBG)

1378

40.9.2 Debug support for timers, watchdog and I

2

C

During a breakpoint, it is necessary to choose how the counter of timers and watchdog

should behave:

• They can continue to count inside a breakpoint. This is usually required when a PWM is

controlling a motor, for example.

• They can stop to count inside a breakpoint. This is required for watchdog purposes.

For the I

2

C, the user can choose to block the SMBUS timeout during a breakpoint.

40.10 DBG registers

40.10.1 DBG device ID code register (DBG_IDCODE)

The STM32G0x1 products integrate a device ID code identifying the device and its die

revision.

This code is accessible by the software debug port (two pins) or by the user software.

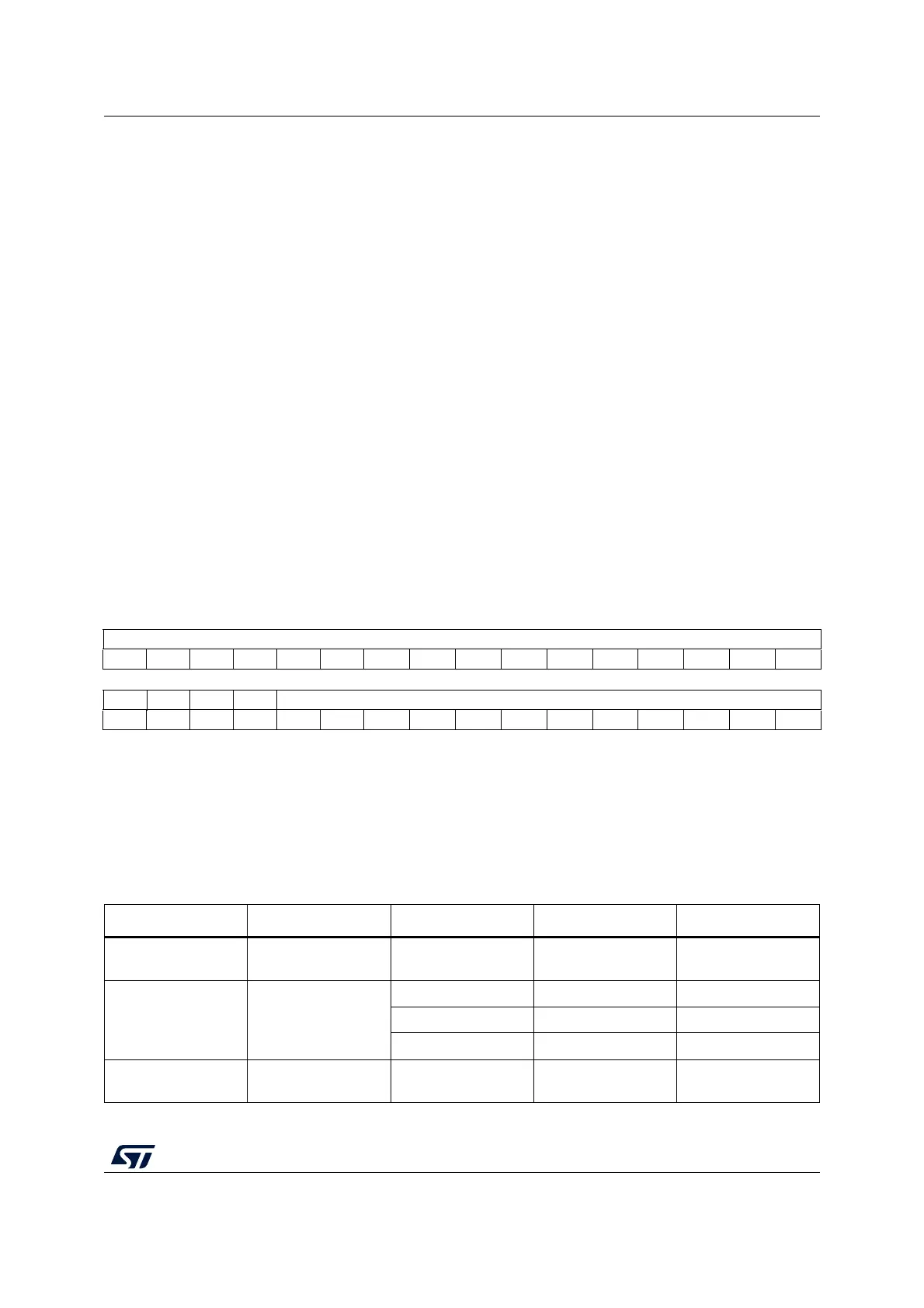

DBG_IDCODE

Address offset: 0x00

Only 32-bit access supported. Read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REV_ID

rrrrrr r r r r rrrrrr

1514131211109876543210

Res. Res. Res. Res. DEV_ID

rrrrrrrrrrrr

Bits 31:16 REV_ID[15:0] Revision identifier

This field indicates the revision of the device. Refer to Table 254.

Bits 15:12 Reserved: read 0b0110.

Bits 11:0 DEV_ID[11:0]: Device identifier

This field indicates the device ID. Refer to Table 254.

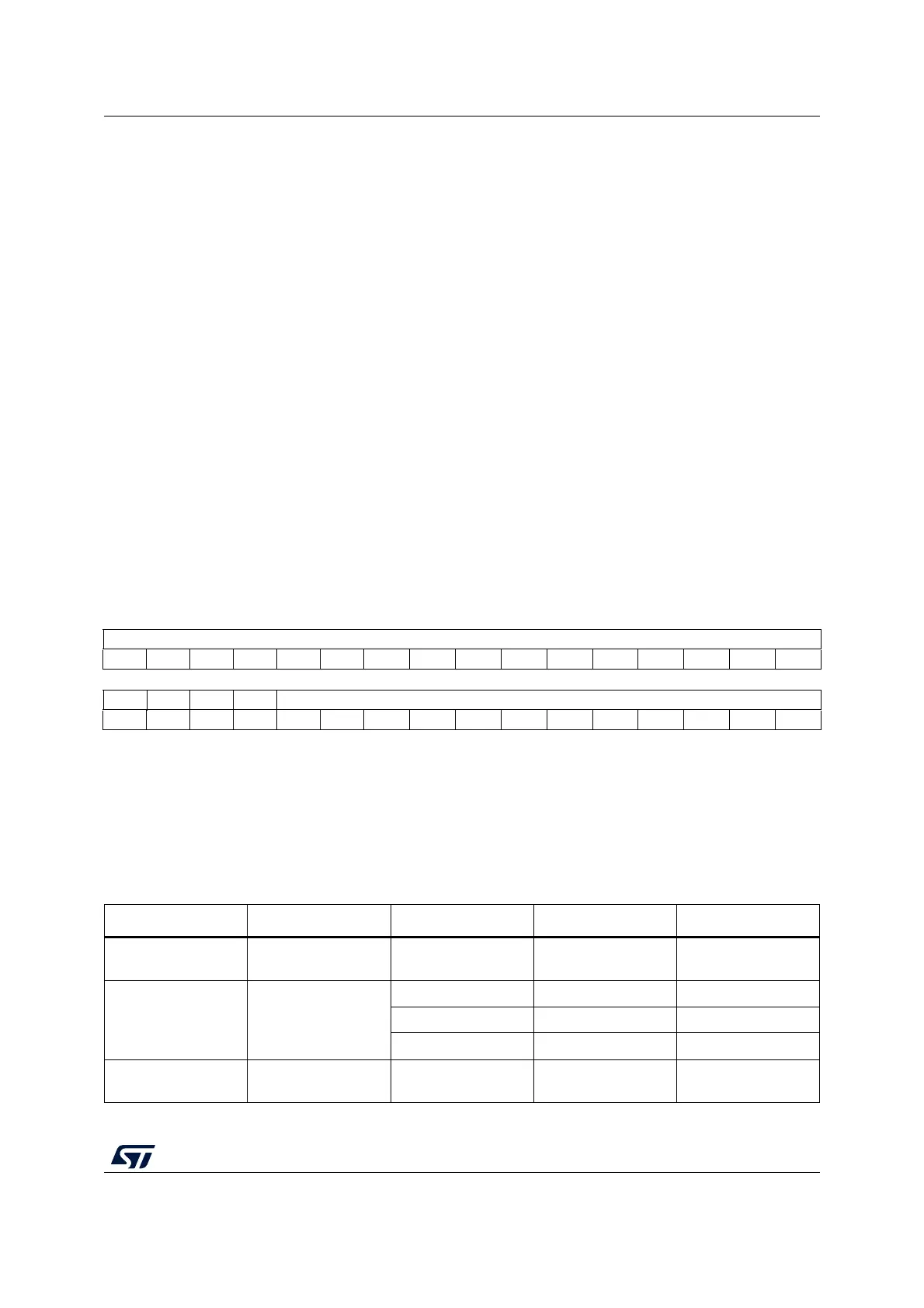

Table 254. DEV_ID and REV_ID field values

Device DEV_ID Revision code Revision number REV_ID

STM32G0B1xx and

STM32G0C1xx

0x467 A 1.0 0x1000

STM32G071xx and

STM32G081xx

0x460

A 1.0 0x1000

Z 1.1 0x1000

B 2.0 0x2000

STM32G051xx and

STM32G061xx

0x456 A 1.0 0x1000

Loading...

Loading...