RM0444 Rev 5 351/1390

RM0444 Analog-to-digital converter (ADC)

403

Caution: When selecting CKMODE[1:0] = 11 (PCLK divided by 1), the user must ensure that the

PCLK has a 50% duty cycle. This is done by selecting a system clock with a 50% duty cycle

and configuring the APB prescaler in bypass modes in the RCC (refer to there Reset and

clock controller section). If an internal source clock is selected, the AHB and APB prescalers

do not divide the clock.

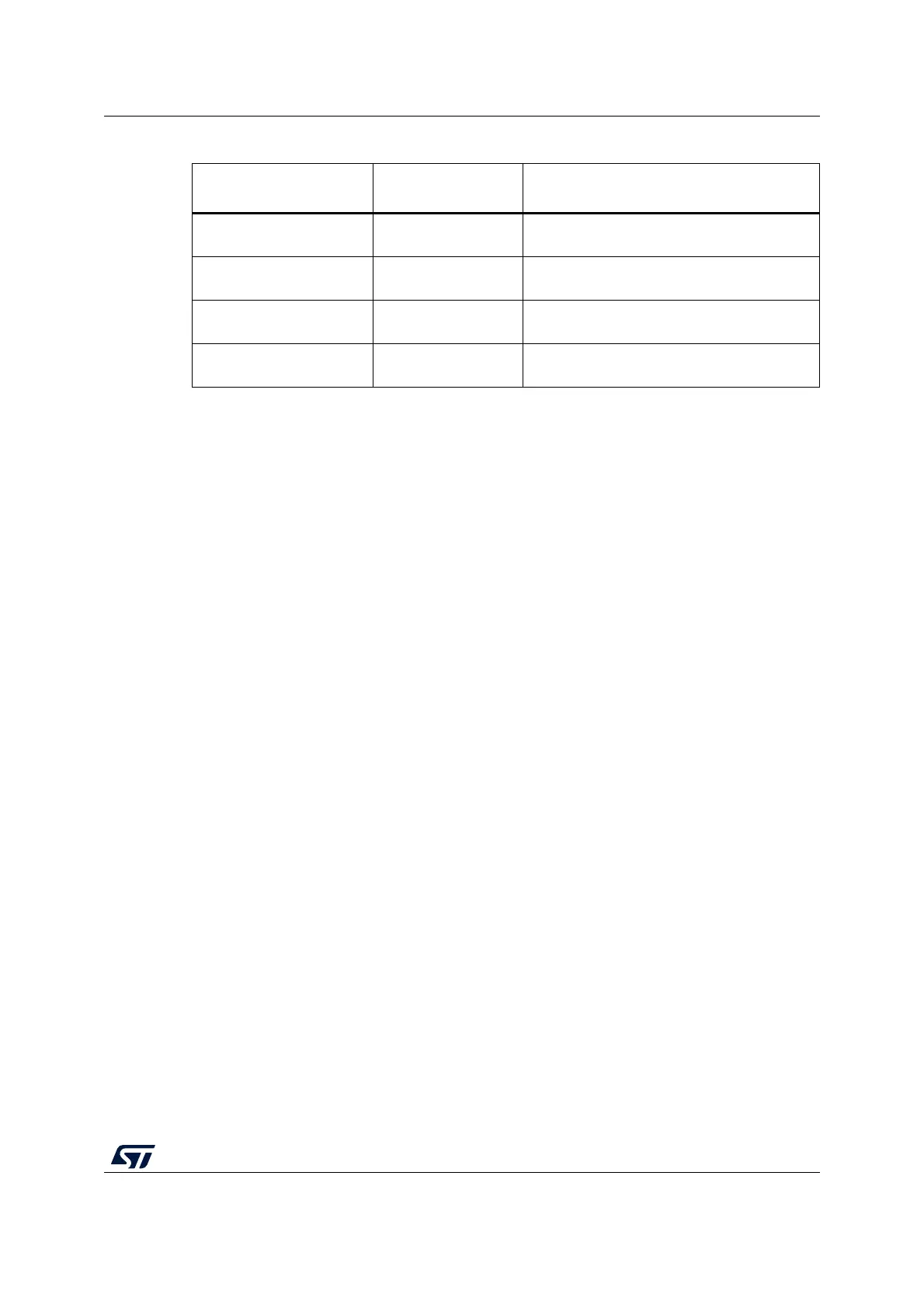

Table 71. Latency between trigger and start of conversion

(1)(2)

1. Refer to the device datasheet for the maximum ADC_CLK frequency.

2. If the trigger is generated by TIM1 or TIM15 clocked at twice the CPU clock frequency, then the latency is

not deterministic and can be increased by one TIM1 or TIM15 clock cycle.

ADC clock source CKMODE[1:0]

Latency between the trigger event

and the start of conversion

HSI16, SYSCLK, or

PLLPCLK

(3)

3. Selected with ADCSEL bitfield of the RCC_CCIPR register.

00 Latency is not deterministic (jitter)

PCLK divided by 2 01

Latency is deterministic (no jitter) and equal to

3.25 ADC clock cycles

PCLK divided by 4 10

Latency is deterministic (no jitter) and equal to

3.125 ADC clock cycles

PCLK divided by 1 11

Latency is deterministic (no jitter) and equal to

3.5 ADC clock cycles

Loading...

Loading...