RM0444 Rev 5 947/1390

RM0444 Inter-integrated circuit (I2C) interface

997

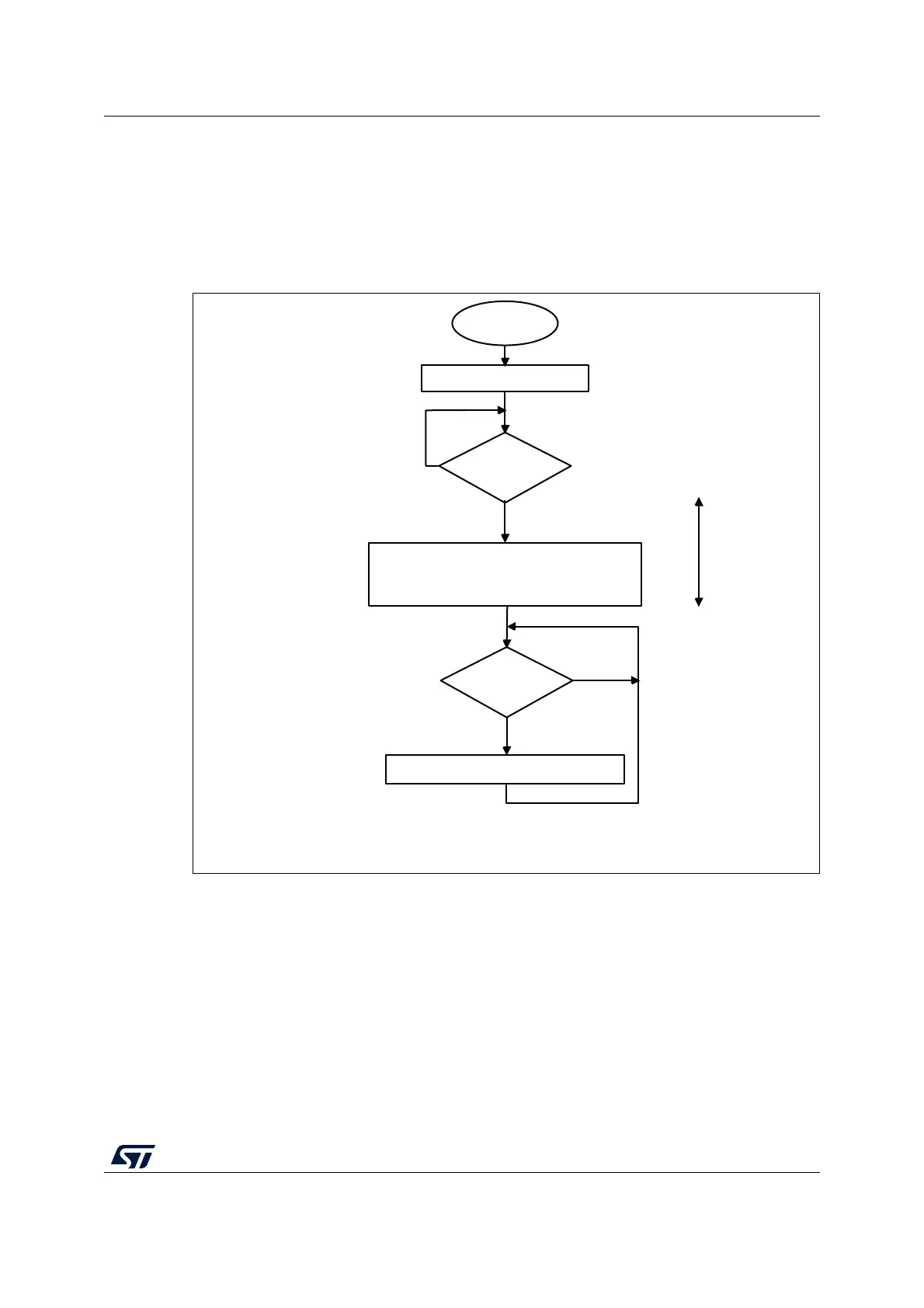

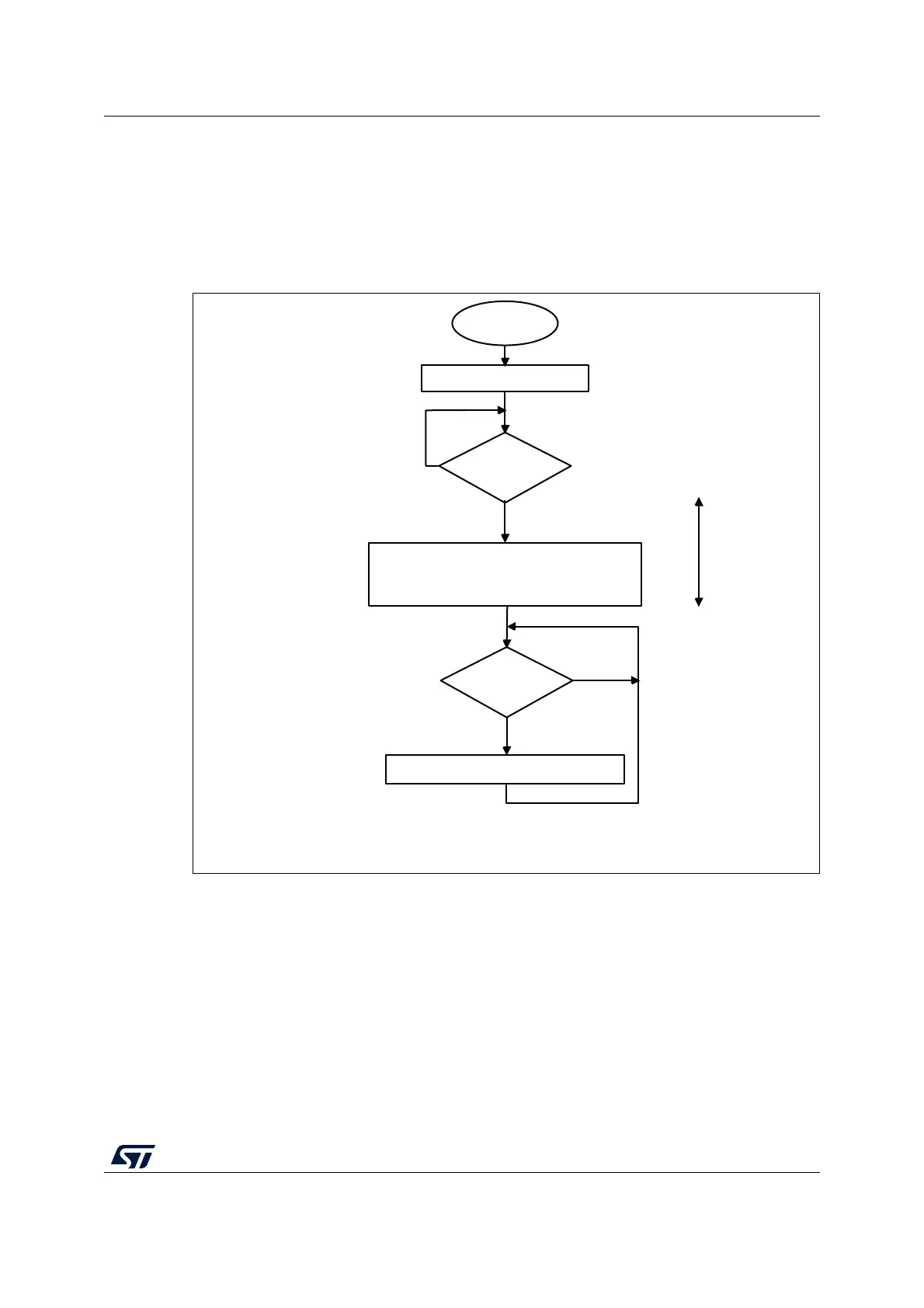

Slave receiver

RXNE is set in I2C_ISR when the I2C_RXDR is full, and generates an interrupt if RXIE is

set in I2C_CR1. RXNE is cleared when I2C_RXDR is read.

When a STOP is received and STOPIE is set in I2C_CR1, STOPF is set in I2C_ISR and an

interrupt is generated.

Figure 294. Transfer sequence flowchart for slave receiver with NOSTRETCH=0

MS19855V2

Slave initialization

Slave reception

Read ADDCODE and DIR in I2C_ISR

Set I2C_ICR.ADDRCF

Write I2C_RXDR.RXDATA

I2C_ISR.ADDR

=1?

No

Yes

I2C_ISR.RXNE

=1?

Yes

No

SCL

stretched

Loading...

Loading...