Real-time clock (RTC) RM0444

890/1390 RM0444 Rev 5

30.5 RTC interrupts

The interrupt channel is set in the masked interrupt status register. The interrupt output is

also activated.

30.6 RTC registers

Refer to Section 1.2 on page 53 of the reference manual for a list of abbreviations used in

register descriptions.

The peripheral registers can be accessed by words (32-bit).

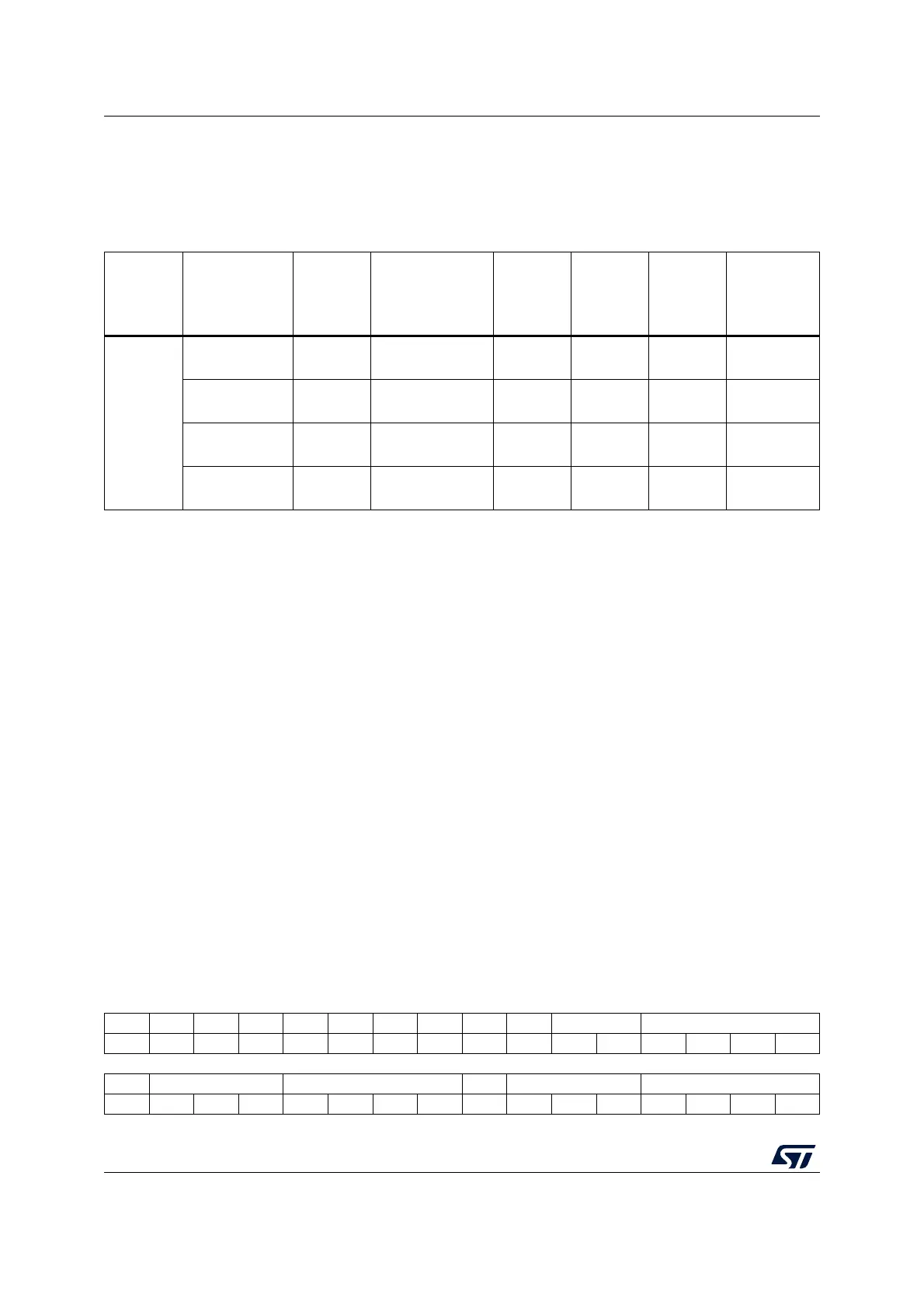

30.6.1 RTC time register (RTC_TR)

The RTC_TR is the calendar time shadow register. This register must be written in

initialization mode only. Refer to Calendar initialization and configuration on page 881 and

Reading the calendar on page 883.

This register is write protected. The write access procedure is described in RTC register

write protection on page 881.

Address offset: 0x00

Backup domain reset value: 0x0000 0000

System reset value: 0x0000 0000 (when BYPSHAD = 0, not affected when BYPSHAD = 1)

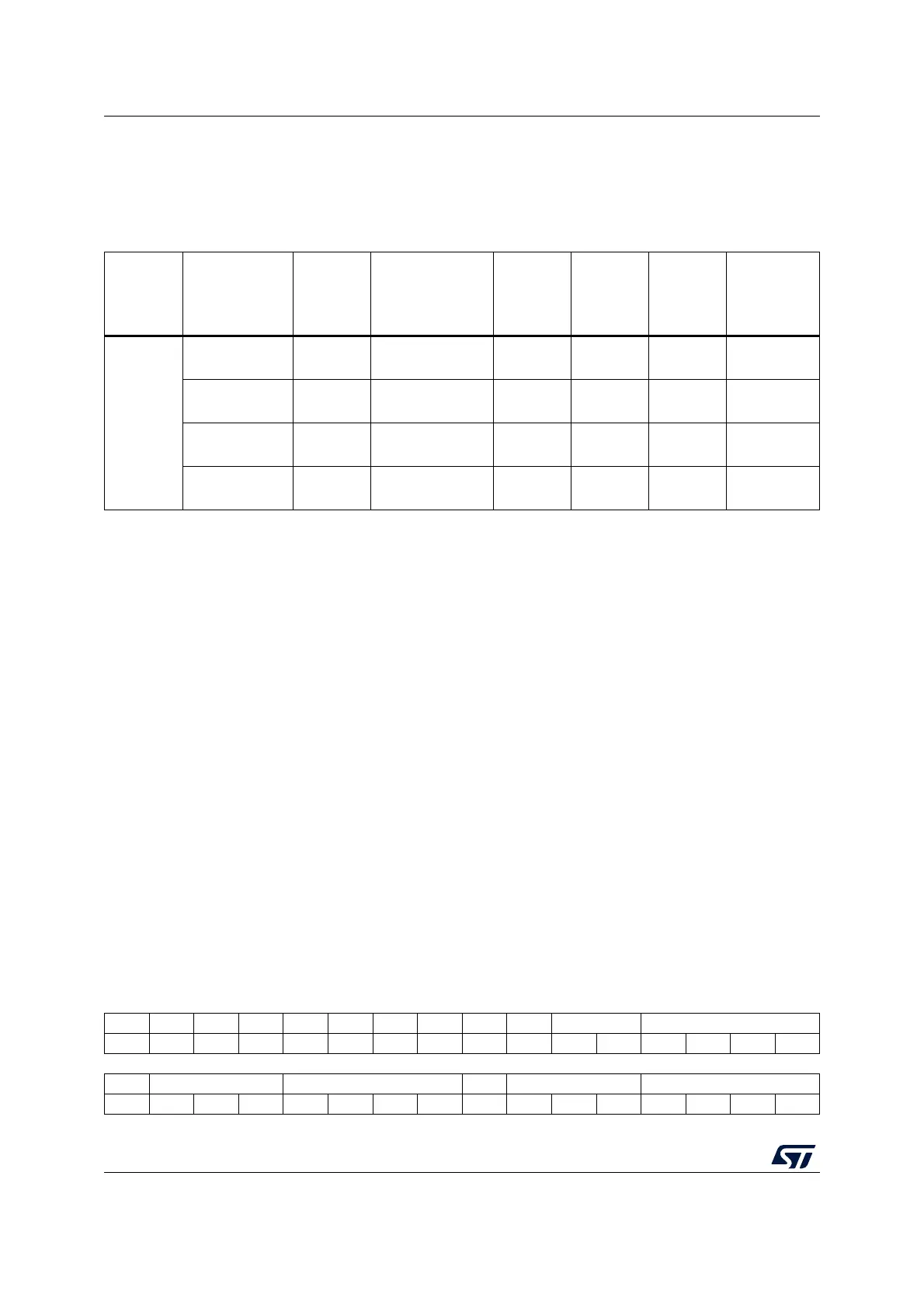

Table 153. Interrupt requests

Interrupt

acronym

Interrupt event

Event

flag

(1)

Enable

control bit

(2)

Interrupt

clear

method

Exit from

Sleep

mode

Exit from

Stop and

Standby

mode

Exit from

Shutdown

mode

RTC

Alarm A ALRAF ALRAIE

write 1 in

CALRAF

Yes Yes

(3)

Yes

(4)

Alarm B ALRBF ALRBIE

write 1 in

CALRBF

Yes Yes

(3)

Yes

(4)

Timestamp TSF TSIE

write 1 in

CTSF

Yes Yes

(3)

Yes

(4)

Wakeup timer

interrupt

WUTF WUTIE

write 1 in

CWUTF

Yes Yes

(3)

Yes

(4)

1. The event flags are in the RTC_SR register.

2. The interrupt masked flags (resulting from event flags AND enable control bits) are in the RTC_MISR register.

3. Wakeup from Stop and Standby modes is possible only when the RTC clock source is LSE or LSI.

4. Wakeup from Shutdown modes is possible only when the RTC clock source is LSE.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. PM HT[1:0] HU[3:0]

rw rw rw rw rw rw rw

1514131211109876543210

Res. MNT[2:0] MNU[3:0] Res. ST[2:0] SU[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...